# Computer Organization and Architecture/Introduction to Computer Organization and Architecture

DCAP502/DCAP206

**Editor Dr. Manmohan Sharma**

# COMPUTER ORGANIZATION AND ARCHITECTURE/INTRODUCTION TO COMPUTER ORGANIZATION AND ARCHITECTURE

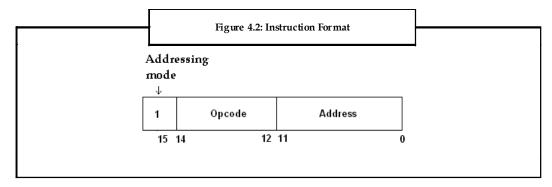

Edited By

Dr. Manmohan Sharma

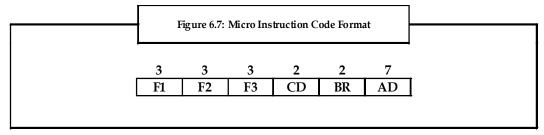

ISBN: 978-93-87034-67-9

# Printed by EXCEL BOOKS PRIVATE LIMITED Regd. Office: E-77, South Ext. Part-I, Delhi-110049

Corporate Office: 1E/14, Jhandewalan Extension, New Delhi-110055

info@excelbooks.com/projects@excelbooks.com internationalalliance@excelbooks.com

for Lovely Professional University Phagwara

### **CONTENTS**

| Unit 1:         | Review of Basics of Digital Electronics  Anuj Sharma, Lovely Professional University   | 1   |

|-----------------|----------------------------------------------------------------------------------------|-----|

| Unit 2:         | Devices Used in Digital Electronics Sahil Rampal, Lovely Professional University       | 23  |

| Unit 3:         | Data Representation and Data Transfer  Yadwinder Singh, Lovely Professional University | 43  |

| Unit 4:         | Computer Organization I<br>Avinash Bhagat, Lovely Professional University              | 65  |

| Unit 5:         | Computer Organization II<br>Avinash Bhagat, Lovely Professional University             | 81  |

| Unit 6:         | Control Unit<br>Pooja Gupta, Lovely Professional University                            | 95  |

| Unit 7:         | Central Processing Unit<br>Manmohan Sharma, Lovely Professional University             | 111 |

| Unit 8:         | Addressing Modes<br>Ajay Kirani Khuswaha, Lovely Professional University               | 125 |

| Unit 9:         | Computer Arithmetic I<br>Sarabjit Kumar, Lovely Professional University                | 143 |

| Unit 10:        | Computer Arithmetic II<br>Avinash Bhagat, Lovely Professional University               | 155 |

| Unit 11:        | Input/Output Organization Ajay Kumar Bansal, Lovely Professional University            | 165 |

| Unit 12:        | Memory Organization Concepts Pooja Gupta, Lovely Professional University               | 185 |

| Unit 13:        | Multiprocessors<br>Manmohan Sharma, Lovely Professional University                     | 205 |

| <b>Unit 14:</b> | Introduction to Parallel Processing  Yadwinder Singh, Lovely Professional University   | 229 |

### **SYLLABUS**

## Computer Organization and Architecture/Introduction to Computer Organization and Architecture

*Objectives:* The objectives of this course are:

- To understand how computers are constructed out of a set of functional units

- To understand how these functional units operate, interact and communicate

- To understand the factors and trade-offs that affect computer performance

- To understand concrete representation of data at the machine level

- To understand how computations are actually performed at the machine level

- To understand how problems expressed by humans are expressed as binary strings in a machine

### DCAP502 COMPUTER ORGANIZATION AND ARCHITECTURE

| Sr. No. | Description                                                                                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.      | <b>Review of Basics of Digital Electronics:</b> Codes, logic gates, flip flops, registers, counters, multiplexer, demultiplexer, decoder, and encoder.                                                                                                                                           |

| 2.      | Integers Representation: Signed Magnitude, 1s & 2s Complement) & Real numbers (Fixed point & Floating Point representation), Register Transfer and Micro operations: Register transfer language Bus & memory transfer, logic micro operation, shift micro operation, Arithmetic Logic Shift Unit |

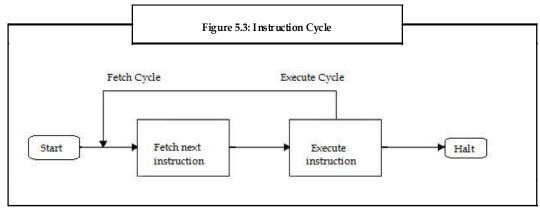

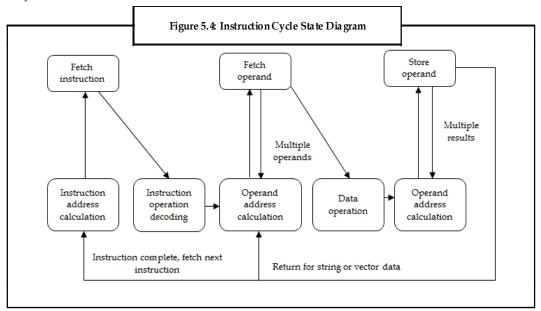

| 3.      | Basic Computer Organization: Instruction codes, computer instructions, timing & control, instruction cycles                                                                                                                                                                                      |

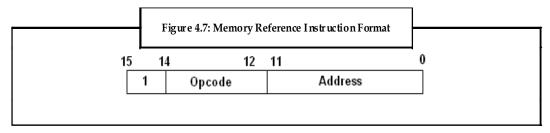

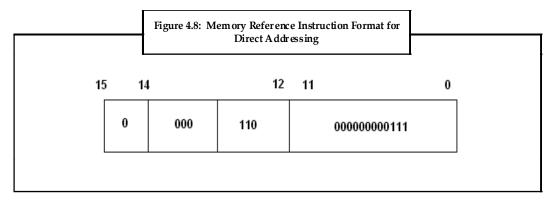

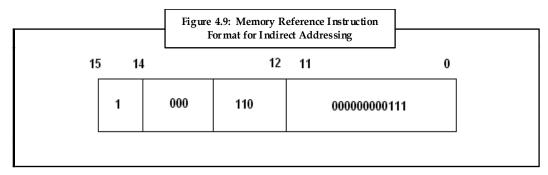

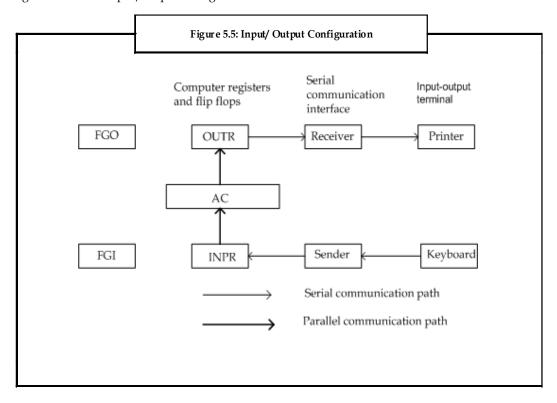

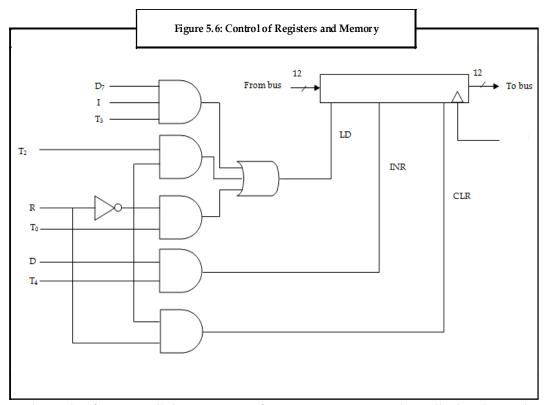

| 4.      | Memory reference instruction, Input/output & interrupts, Design of basic computer Control Unit:<br>Hardwired vs. micro programmed control unit, Control Memory, Address Sequencing, Micro program Sequencer                                                                                      |

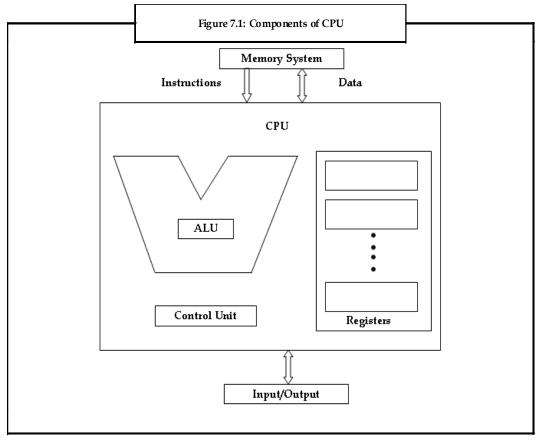

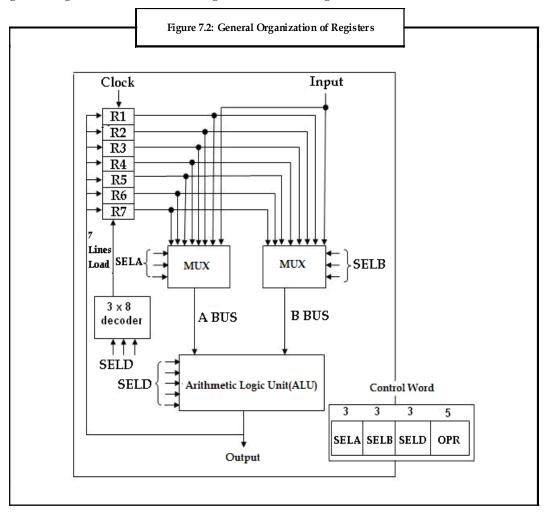

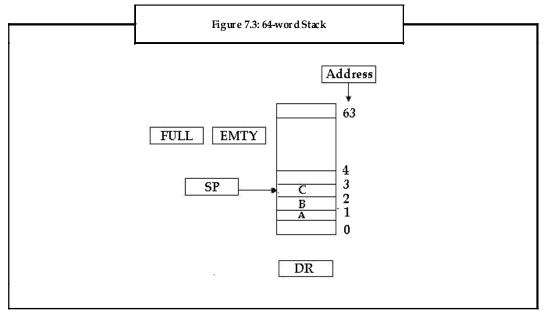

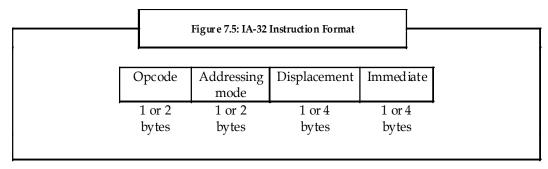

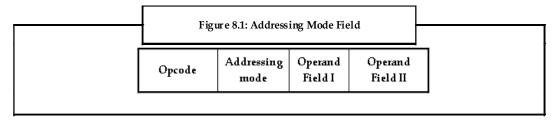

| 5.      | Central Processing Unit: General register organization, stack organization, instruction format, Addressing Modes Data transfer & manipulation, program control, RISC, CISC.                                                                                                                      |

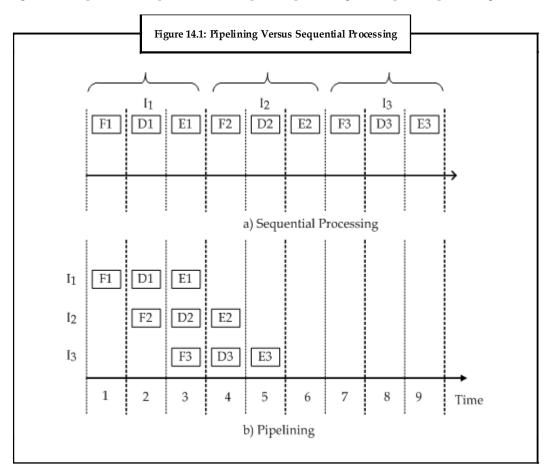

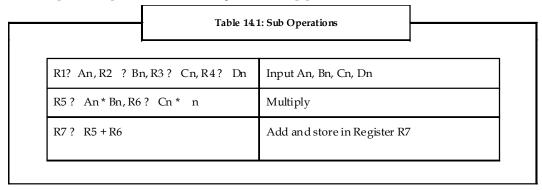

| 6.      | Introduction to Parallel Processing: Pipelining, Instruction pipeline, RISC Pipeline, Vector Processing                                                                                                                                                                                          |

| 7.      | Computer Arithmetic: Addition, Subtraction, Multiplication & Division Algorithm(s), Decimal arithmetic units & Operations.                                                                                                                                                                       |

| 8.      | <b>Input-Output Organization:</b> Peripheral devices, I/O interface, data transfer schemes, program control, interrupt, DMA transfer, I/O Processor                                                                                                                                              |

| 9.      | Memory Organization Concepts: Cache & Virtual memory                                                                                                                                                                                                                                             |

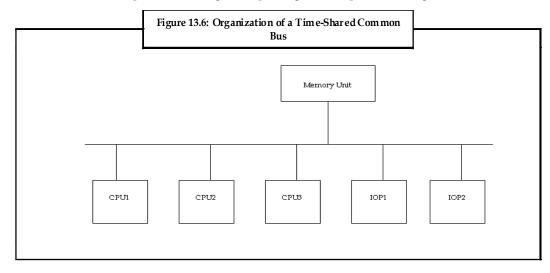

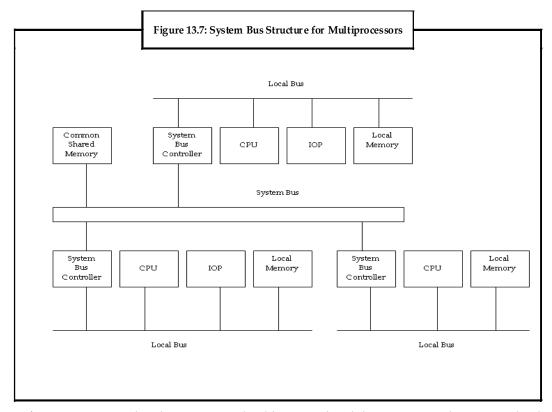

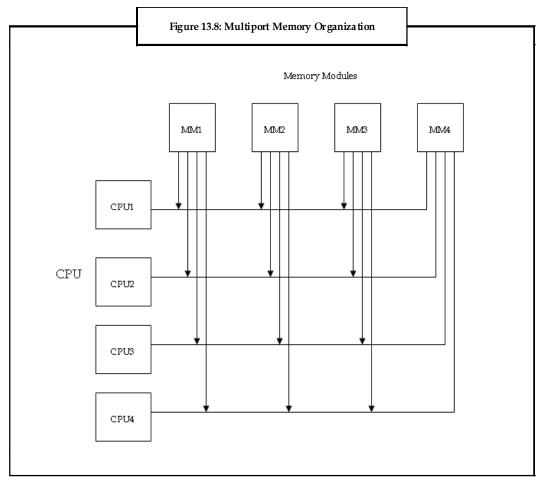

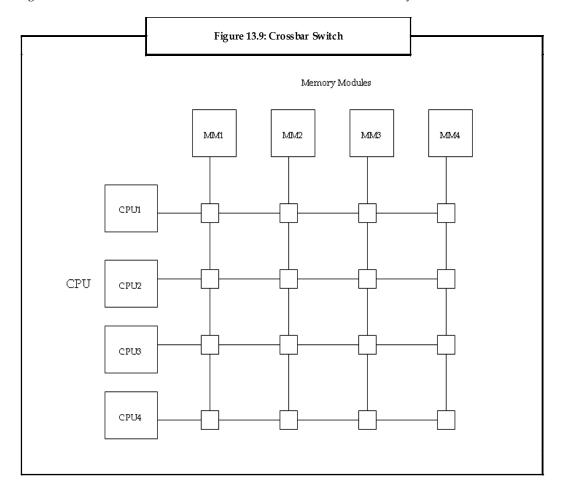

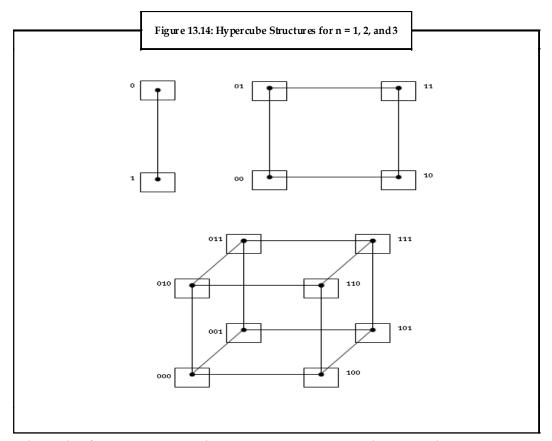

| 10.     | Multiprocessors: Characteristics, Interconnection Structures, Interprocessor Communication and synchronization                                                                                                                                                                                   |

### DCAP206 INTRODUCTION TO COMPUTER ORGANIZATION & ARCHITECTURE

| Sr. No. | Description                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.      | <b>Tools for course understanding:</b> Awareness of ISA bus interface, a popular bus architecture used in IBM and compatible personal computer systems.                                                                                                                                                                                                                                   |

|         | <b>Digital Logic Circuits:</b> Digital computers, Logic gates, Boolean Algebra, Map Simplification, Half Adder, Full Adder, Flip flops – SR, JK, D, T, Edge triggered flip flops, Sequential Circuits                                                                                                                                                                                     |

| 2.      | <b>Digital Components:</b> Integrated circuits, Decoders – NAND gate decoder, Encoders, Multiplexers, Demultiplexers, Registers, Shift registers, Bidirectional Register with parallel load, Binary counters, Memory Unit – RAM, ROM, Types of ROMs                                                                                                                                       |

| 3.      | <b>Data Representation:</b> Number systems – decimal, octal, hexadecimal, Complement – (r-1)'s complement, r's complement, Fixed point representation, floating point representation, Gray code, Decimal codes, alphanumeric codes, Error detection codes                                                                                                                                 |

| 4.      | Register Transfer and Micro-operations: Register transfer language, Register transfer, Bus and memory transfers – three state bus buffers, Arithmetic micro-operations – binary adder, binary adder subtractor, binary incrementer, arithmetic circuit                                                                                                                                    |

| 5.      | Logic micro-operations and its hardware implementation, Shift micro-operations and hardware implementation, Arithmetic Logic Shift unit, Hardware description languages                                                                                                                                                                                                                   |

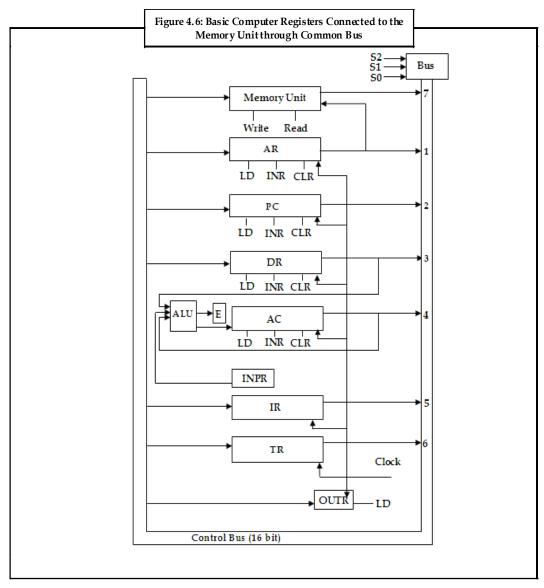

| 6.      | <b>Basic Computer Organization and Design:</b> Instruction Codes, Stored program organization, Computer registers, Common bus system, Computer instructions, Timing and Control, Instruction cycle, Memory reference instructions, Input output and interrupt, complete design of basic computer                                                                                          |

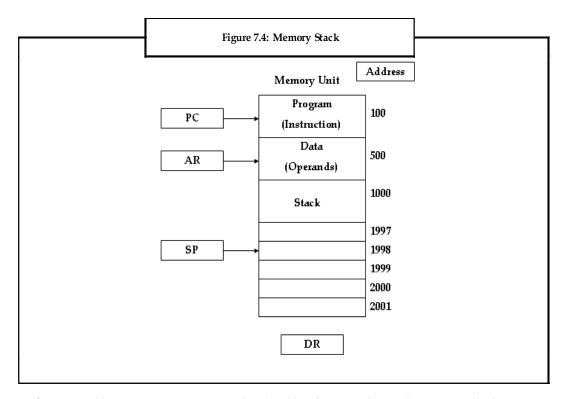

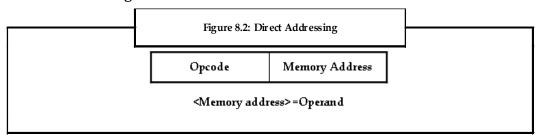

| 7.      | Central Processing Unit: General register organization, control word, Stack organization, register stack, memory stack, Instruction formats – three address, two address, one address, zero address instructions, Addressing modes, Data transfer and manipulation, arithmetic, logical, bit manipulation, Program control, Reduced Instruction Set Computer (RISC), CISC characteristics |

| 8.      | <b>Input-Output Organization:</b> Input output interface, I/O bus and interface modules, I/O vs memory bus, Isolated vs Memory mapped I/O                                                                                                                                                                                                                                                 |

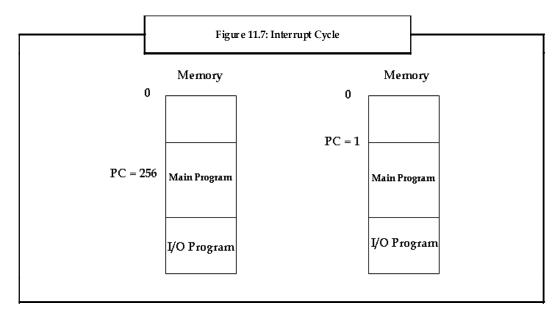

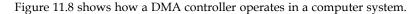

| 9.      | Asynchronous data transfer, handshaking, Programmed I/O, Interrupt-initiated I/O, Priority Interrupt – Daisy chaining, parallel priority, priority encoder, interrupt cycle, DMA controller and transfer                                                                                                                                                                                  |

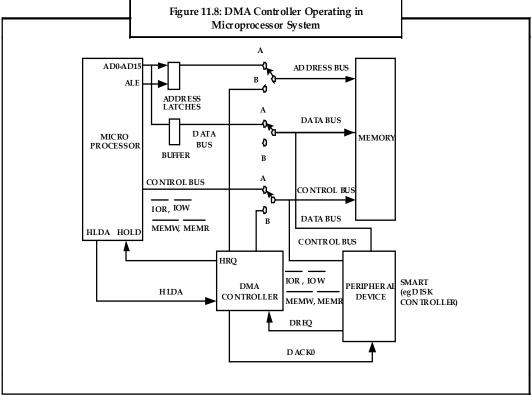

| 10.     | <b>Memory Organization:</b> Memory hierarchy, RAM, ROM chips, memory address map, Associative memory, Cache memory, Virtual memory, Memory management hardware                                                                                                                                                                                                                            |

### **Unit 1: Review of Basics of Digital Electronics**

### CONTENTS

Objectives

Introduction

- 1.1 Codes in Digital Electronics

- 1.1.1 Classification of Binary Codes

- 1.2 Logic Gates

- 1.3 Summary

- 1.4 Keywords

- 1.5 Self Assessment

- 1.6 Review Questions

- 1.7 Further Readings

### **Objectives**

After studying this unit, you will be able to:

- Discuss the codes in digital electronics

- List the functions of different logic gates

- Discuss the truth table for all the logic gates

### Introduction

Digital electronics is a field of computer science. It deals with devices that are used to carry out computer applications.

In digital electronics, we use two-state or binary logic. The two logic states are "0" (low) and "1" (high).

Computer uses binary number system for its operations. Digital electronics represents the two binary numbers, 1 and 0, using two voltage levels in a device called a logic gate. Sometimes the two states can also be represented using Boolean logic functions, "true" or "false" states, or using an "on" or "off" state.

Logic gates are important components of a digital circuit. A logic gate takes two inputs and generates a single output. In this unit we will discuss about the basic logic gates and their corresponding truth tables.

### 1.1 Codes in Digital Electronics

Basically, digital data is represented, stored, and transmitted as groups of binary digits which are called bits. The group of bits is known as binary code. Binary codes are used in computers as they allow computers to perform complex calculations quickly and efficiently. Binary codes are used in financial, commercial, and industrial applications. To understand how binary codes are applied in these fields, we first have to understand the classification of binary codes.

### 1.1.1 Classification of Binary Codes

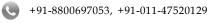

Binary codes can be represented as numbers and letters of the alphabets as well as many special characters and control functions. They are classified as numeric or alphanumeric codes. Numeric codes are used to represent numbers, whereas alphanumeric codes are used to represent alphabetic letters and numerals.

The binary codes are classified as shown in figure 1.1.

As mentioned earlier, numeric codes are used to represent numbers. The following are the numeric codes:

1. Weighted Binary Codes: Weighted binary codes are those which follow the positional weighting principles. In weighted codes, each position of the number represents a specific weight. For example, in decimal code, if the number is 345, then the weight of 3 is 100, 4 is 10, and 5 is 1. In the 8421 weighted binary code, each digit has a weight of 8, 4, 2 or 1 corresponding to its position.

*Example:* The codes 8421, 2421 and 5211 are examples of weighted binary codes.

Non-Weighted Binary Codes: Non-weighted codes do not follow the positional weighting

principles. In non-weighted codes, each digit position within the number does not have any

fixed value.

Example:Excess-3 and Gray codes are examples of non-weighted codes. Excess-3 codes are used to express decimal numbers. The code can be derived from the natural BCD (8421) code by adding 3 (011 in binary) to the coded number. It is used in decimal arithmetic units. The excess-3 code of 1000 in 8421 is 1011. Gray codes represent each number in the sequence of integers {0...2^N-1} as a binary string of length N such that the adjacent integers have Gray code representations which differ in only one bit position.

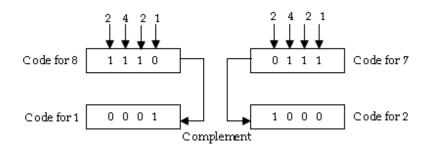

3. **Reflective Codes:** A code is said to be reflective when the code for 9 is complement for the code for 0, 8 for 1, 7 for 2, 6 for 3, and 5 for 4.

Example: Codes 2421 and excess-3 are reflective. In code 2421: we know that the positional weights are 2, 4, 2 and 1. The following figure shows an example of reflective code where the complement of 8 is 1 and the complement of 7 is 2.

4. *Sequential Codes:* Sequential codes are codes in which the succeeding code is one binary number greater than its preceding code. This assists in mathematical data manipulation.

Example: 8421 and excess-3 codes are sequential codes.

5. *Cyclic Codes:* In cyclic codes, only one bit in the code changes at a time while moving from one number to the next. It is a non-weighted code, which means that the position of bit does not contain any weight.

Table1.1 shows the bit patterns assigned for gray code from decimal 0 to 10.

| able 1.1: Decimal Code to Gray Code Conversion |  |  |  |

|------------------------------------------------|--|--|--|

| Gray code                                      |  |  |  |

| 0000                                           |  |  |  |

| 0001                                           |  |  |  |

| 0011                                           |  |  |  |

| 0010                                           |  |  |  |

| 0110                                           |  |  |  |

| 0111                                           |  |  |  |

| 0101                                           |  |  |  |

| 0100                                           |  |  |  |

| 1100                                           |  |  |  |

| 1101                                           |  |  |  |

| 1111                                           |  |  |  |

|                                                |  |  |  |

Error Detecting Codes: Whenever data is transmitted from one point to another, there is a

probability that the data may get corrupted. In order to detect these data errors, some special

codes called error detection codes are used.

7. *Error Correcting Codes:* These codes not only detect errors in data, but also correct them significantly. Error correction codes are a method by which a set of symbols can be represented such that even if any 1 bit of the representation gets accidentally flipped, we can still clearly identify the earlier symbol. Error correcting codes depend mainly on the notations and results of linear algebra. Error correction can be done using many methods like parity checking, Hamming codes, Single-bit Error Correction Double-bit Error Correction (SECDED), and so on.

Notes Error correcting codes are used in memories, networking, CDROM, and so on.

Example: Error correction using parity checking is as follows:

In parity check, an extra bit is added to the binary number to make all the digits in the binary number to sum up to an even or odd value. When the number adds up to an even number, we call it even parity and when the number sums up to an odd number, we call it odd parity. Consider the following two binary numbers:

1011010

1101011

Now, if we want to use even parity, we can add a parity bit to these numbers to obtain an even number as shown below:

01011010 4

11101011 6

If we want to use odd parity, we can add a parity bit to the number as follows:

11011010 5

01101011 5

Most of the modern applications use even parity. Let us consider even parity in our example.

The two binary numbers that need to be transmitted are:

01011010......The even parity

11101011.....The even parity

Suppose during transmission the bits get changed as follows:

01111010 5

10101011 5

We can observe that the digits in the number sum up to odd numbers. Since we are using even parity, the computer knows that there is an error in the transmission.

- 8. *Alphanumeric Codes*: These are codes that consist of both numbers and alphabets. The most commonly used alphanumeric codes are ASCII and EBCDIC.

- (a) *EBCDIC Code:* EBCDIC (Extended Binary Coded Decimal Interchange) is mainly used with large computer systems like mainframe computers. It is an 8-bit code which accommodates up to 256 characters.

(b) ASCII Code: ASCII (American Standard Code for Information Interchange) has become a standard alphanumeric code for microcomputers and computers. It is a 7-bit code, which represents 128 different characters. These 128 characters include 52 alphabets, which include A to Z and a to z, numbers from 0 to 9 (that is, 10 numbers), 33 special characters and symbols, and 33 control characters.

Notes

### 1.2 Logic Gates

A logic gate is an electronic device that makes logical decisions based on the different combinations of digital signals available on its inputs. A digital logic gate can have more than one input signal but has only one digital output signal.

Integrated Circuits or ICs can be grouped together into families according to the number of transistors or gates. Integrated circuits are categorized according to the number of logic gates or the circuit complexities within a chip.

### **AND Gate**

AND gate is a type of digital logic gate, which has an output that is normally at logic level "0" and goes "HIGH" to a logic level "1" when all of its inputs are at logic level "1". The output of AND gate returns "LOW" when any of its inputs are at a logic level "0".

The Boolean expression for AND gate is Q= A.B.

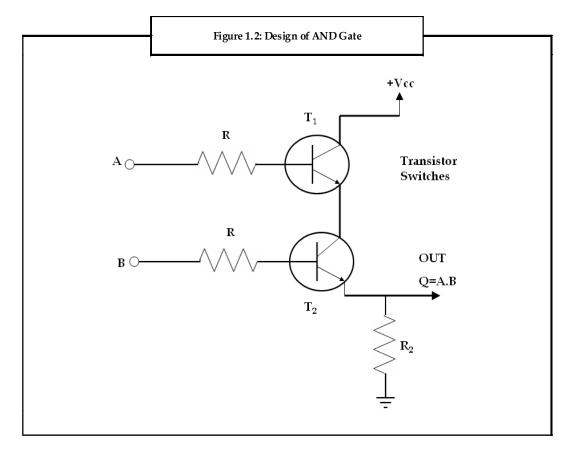

A simple 2-input logic AND gate can be constructed using RTL structure connected together as shown below in figure 1.2. Both transistors,  $T_1$  and  $T_2$  must be saturated "ON" to produce an output at Q. In the figure 1.2, we can observe that the output from  $T_1$  is the input to  $T_2$ . Vcc is the input to transistor 1 and the final output, Q=A.B, is obtained from  $T_2$ .

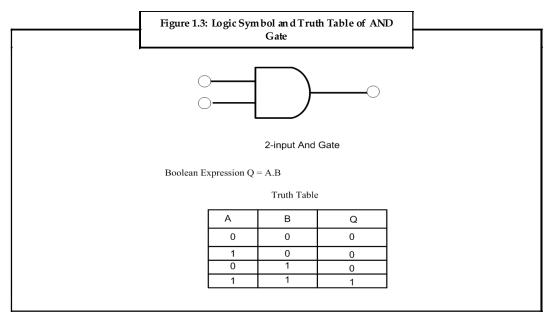

The figure 1.3 shows the truth table and symbol of AND gate.

F

Example: Commonly available digital logic AND gate ICs are:

TTL Logic Types

74LS08 Quad 2-input CMOS Logic Types

74LS11 Triple 3-input

CD4081 Quad 2-input

74LS21 Dual 4-input

CD4073 Triple 3-input

Internal structure of IC 7408

CD4082 Dual 4-input

6

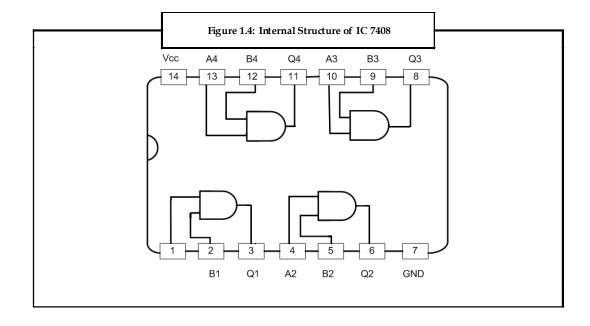

The figure 1.4 depicts how AND gates are placed within an IC. In the figure, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the AND gate, while 3, 6, 8, and 11 are the AND outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

### **OR Gate**

OR gate is a type of digital logic gate which has an output that is normally at logic level '0', but goes 'HIGH' to a logic level '1' when any of its inputs are at logic level '1'. The output of a logic OR gate returns 'LOW' again when all of its inputs are at a logic level '0'.

The Boolean expression for OR gate is denoted as Q = A + B.

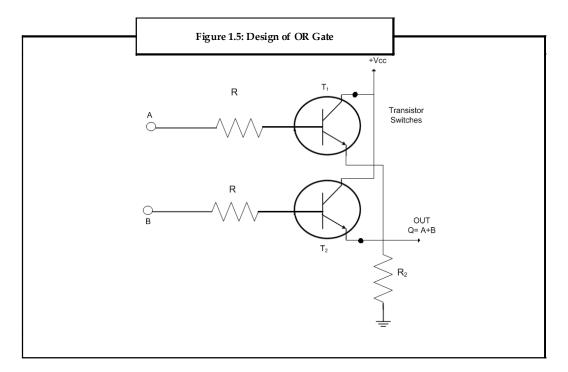

A simple 2-input logic OR gate can be constructed using RTL structure connected together as shown in the figure 1.5 Either transistor  $T_1$  or transistor  $T_2$  must be saturated "ON" to produce an output at Q. In the figure 1.5, we can observe that Vcc is the input to both  $T_1$  and  $T_2$ . The output of  $T_1$  and  $T_2$  constitutes the final output - Q=A+B.

Example: Commonly available OR gate ICs are as follows:

TTL Logic Types CMOS Logic Types

74L S32 Quad 2-input CD4071 Quad 2-input CD4075 Triple 3-input CD4072 Dual 4-input

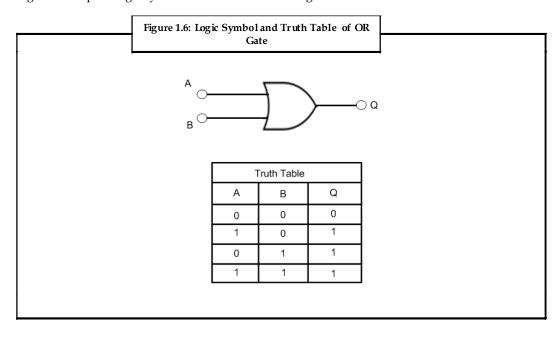

Figure 1.6 depicts logic symbol and truth table of OR gate.

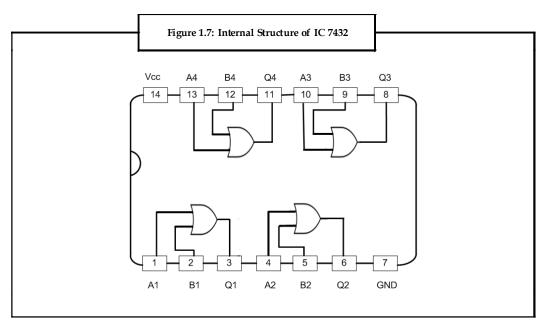

Figure 1.7 depicts how OR gates are placed within an IC.

In the figure, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the OR gate, while 3, 6, 8, and 11 are the OR outputs. Pin number 7 is connected to the ground and pin number 14 is connected to the power supply.

### **NOT Gate**

In digital electronics, the NOT gate is also known as inverting buffer or a digital inverter element. A NOT gate is basically a single input device. It has an output level that is often at logic level '1'. However, it goes 'LOW' to a logic level '0' whenever the single input is at logic level '1'. The output from a NOT gate returns 'HIGH' when its input is at logic level '0'.

The Boolean expression of NOT gate is  $Q=\overline{A}$

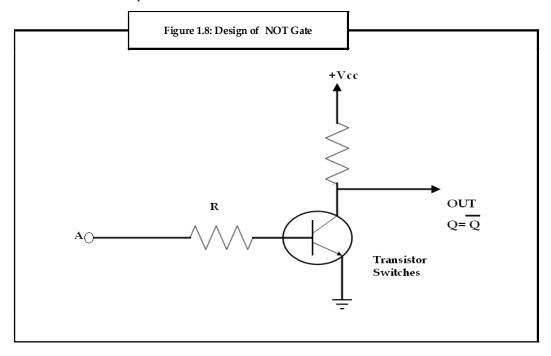

A simple 2-input logic NOT gate can be constructed using a RTL structure as shown in figure 1.8 with the input connected directly to the transistor base. If the transistor is saturated 'ON', we receive an inversed output 'OFF' at Q.

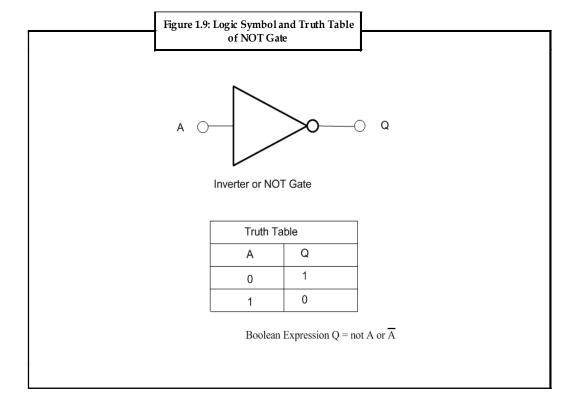

Figure 1.9 depicts the logic symbol and the truth table of a NOT gate.

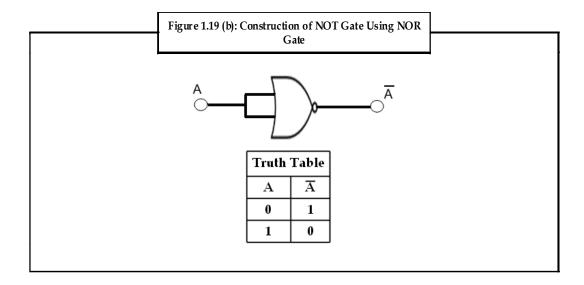

### Notes NAND and NOR Gate Equivalents for NOT Gate

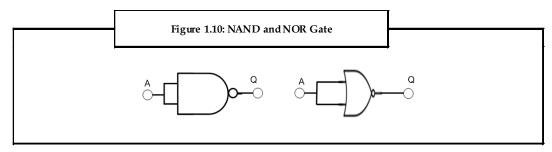

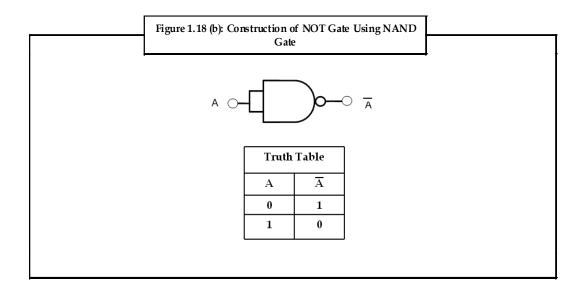

A NOT gate can be constructed using standard NAND and NOR gates by connecting all their inputs together to a common input signal as shown in figure 1.10.

Example: Commonly available logic NOT gate and Inverter IC's are as follows:

TTL Logic Types

74LS04 Hex Inverting NOT Gate

74LS04 Hex Inverting NOT Gate

74LS14 Hex Schmitt Inverting NOT Gate

74LS1004 Hex Inverting Drivers

CMOS Logic Types CD4009 Hex Inverting NOT Gate CD4069 Hex Inverting NOT Gate

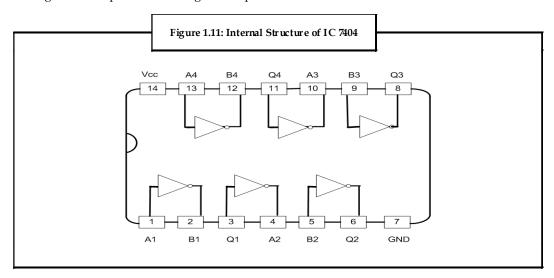

The figure 1.11 depicts how NOT gates are placed within an IC.

In the figure, pin number 1, 3, 5, 9, 11, and 13 are the inputs to the NOT gate, while 2, 4, 6, 8, 10, and 12 are the NOT outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

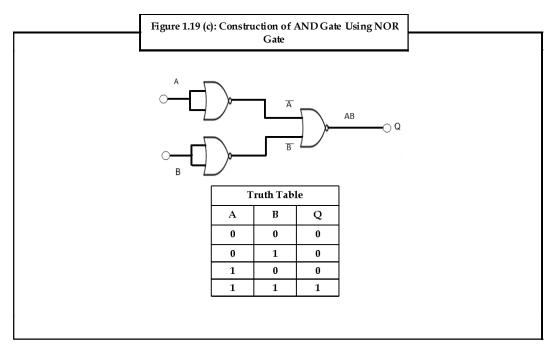

### **Universal Gates**

NAND gate and NOR gate are called universal gates because these gates can be connected together in various combinations to form other gates like AND, OR, and NOT.

### **NAND** Gate

NAND gate is a combination of AND gate with an inverter or NOT gate connected together in series. NAND gate has an output that is normally at logic level '1' and only goes 'LOW' to logic level '0' when all of its inputs are at logic level "1".

The Boolean expression of NAND gate is  $Q = \overline{A.B}$

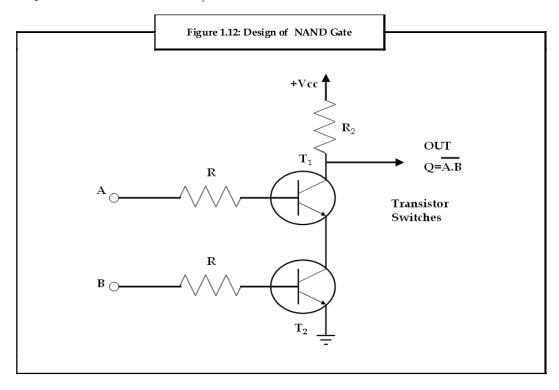

A simple 2-input logic NAND gate can be constructed using RTL structure connected together as shownin figure 1.12, with the inputs connected directly to the transistor bases. Either transistor  $T_1$  or  $T_2$  must be cut-off 'OFF' to receive an output at Q. Figure 1.12 depicts a design of NAND gate. In figure 1.12, we can observe that the output of transistor  $T_1$  is the input to transistor  $T_2$ . The output,  $Q = \overline{A.B}$  is received from  $T_1$ .

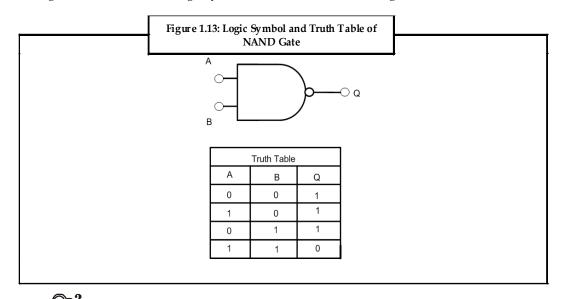

The figure 1.13 illustrates the logic symbol and truth table of NAND gate.

Did u know? NAND gate and NOR gate are called universal gates because these gates can be connected together in various combinations to form other gates like AND, OR, and NOT gates.

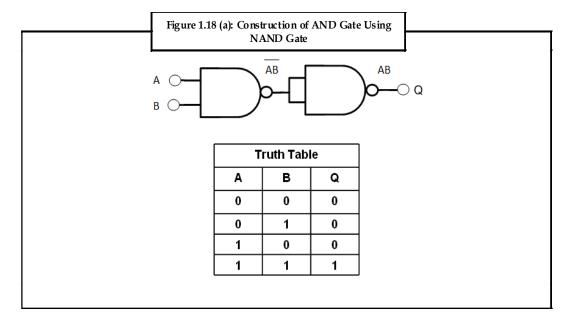

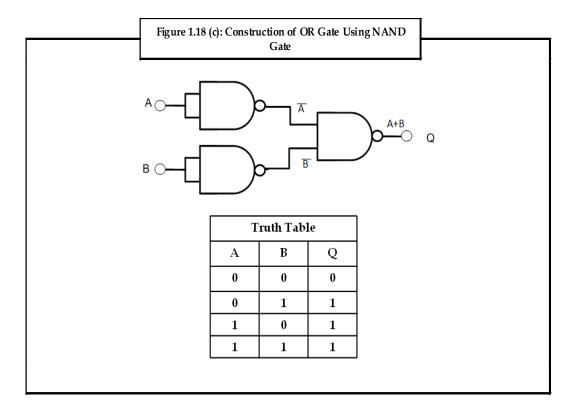

The various logic gates formed using NAND gates are as follows:

Example: Commonly available logic NAND gate ICs are as follows:

TTL Logic Types

74LS00 Quad 2-input

74LS10 Triple 3-input

74LS20 Dual 4-input

74LS30 Single 8-input

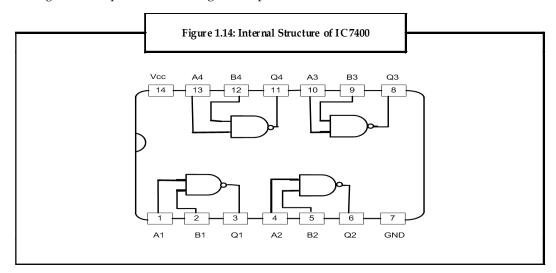

The figure 1.14 depicts how NAND gates are placed within an IC.

In the figure, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the NAND gate, while 3, 6, 8, and 11 are the NAND outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

### **NOR Gate**

NOR gate is a combination of OR gate with a NOT gate connected together in a series. The NOR gate has an output that is normally at logic level '1' and only goes 'LOW' to logic level '0' when any of its inputs are at logic level '1'.

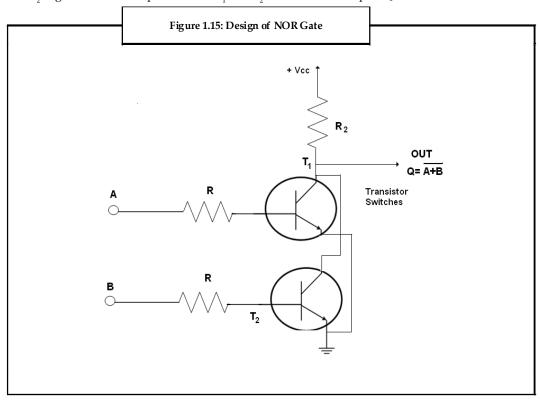

The Boolean expression of NOR gate is Q= A+B

To construct a 2-input logic NOR gate, an RTL Resistor-transistor switches can be used. The RTL must be connected together as shown in the figure 1.15 with the inputs connected directly to the transistor bases. Both transistors,  $T_1$  and  $T_2$  must be cut-off 'OFF' to receive an output at Q. Figure 1.15 shows the design of NOR gate.

In figure 1.15, we can observe that Vcc is the input to both transistors  $T_1$  and  $T_2$ . The output of  $T_1$  and  $T_2$  is grounded. The inputs of both  $T_1$  and  $T_2$  constitute the output, Q=A+B.

Notes

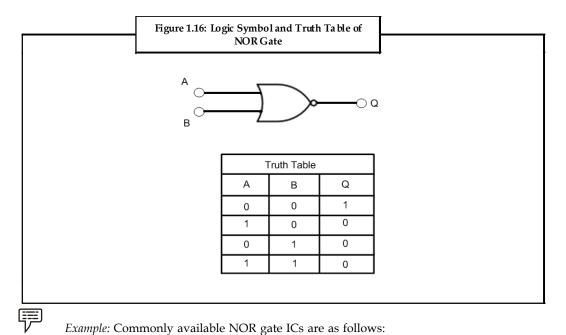

Figure 1.16 depicts the logic symbol and truth table of NOR gate.

TTL Logic Types 74LS02 Quad 2-input 74LS27 Triple 3-input 74LS260 Dual 4-input CMOS Logic Types CD4001 Quad 2-input CD4025 Triple 3-input CD4002 Dual 4-input

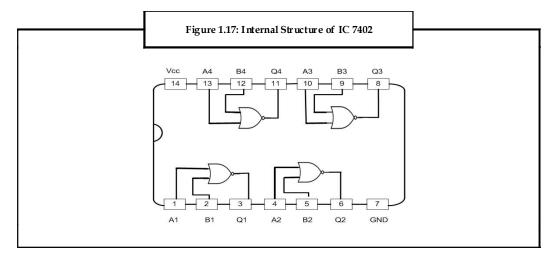

Figure 1.17 shows the internal structure of IC 7402.

Figure 1.17 depicts how NOR gates are placed within an IC. In the figure 1.17, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the NOR gate, while 3, 6, 8, and 11 are the NOR outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

### **Application of Universal Gates**

The NAND and NOR gates can be used to construct other forms of gates. The figures 1.18(a), 1.18 (b), 1.18 (c) depict the application of these universal gates.

The various logic gates formed using NAND gates and their truth tables are as follows:

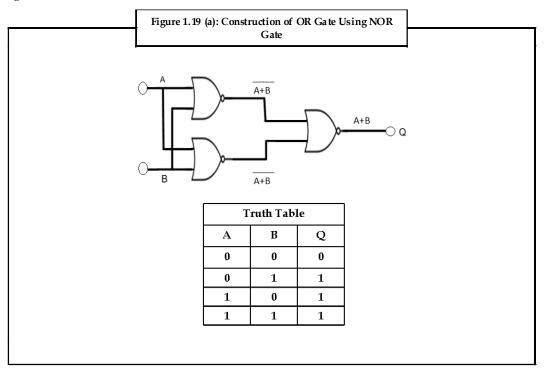

### Notes NOR gates

The construction of logic gates using NOR gates and their truth tables are given in the below figures.

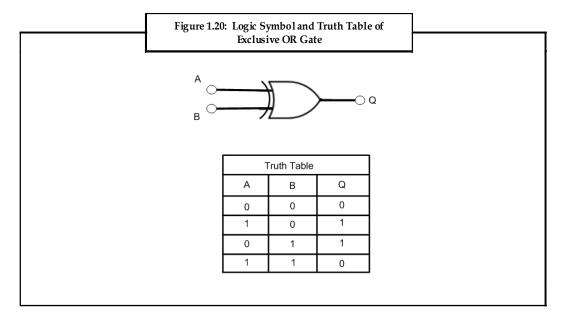

### **Exclusive-OR Gate**

The output of an Exclusive-OR gate goes 'HIGH' when its two input terminals are at different logic levels with respect to each other and they can be at logic level '1' or both at logic level '0'.

The Boolean expression is  $Q = (A \oplus B) = A.B + A.B$

One of the main disadvantages of implementing the Ex-OR function is that it contains three different types of logic gates OR, NAND, and AND within its design.

One simpler way of producing the Ex-OR function from a single gate is to use NAND gate as shown below.

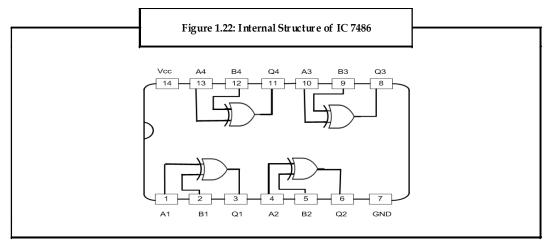

Example: Some of the commonly available Exclusive-OR gate ICs are as follows:

TTL Logic Types 74LS86 Quad 2-input CMOS Logic Types CD4030 Quad 2-input

The figure 1.22 depicts how Ex-OR gates are placed within an IC.

In the figure, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the Ex-OR gate, while 3, 6, 8, and 11 are the Ex-OR outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

### **Exclusive-NOR Gate**

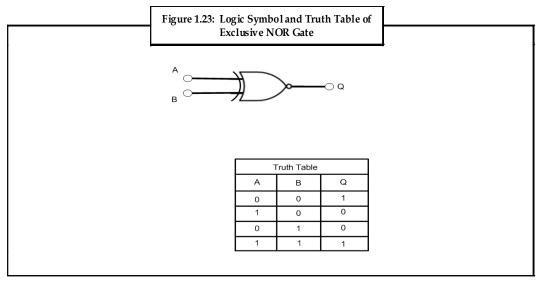

The Exclusive-NOR gate function is a digital logic gate that is the complementary form of the Exclusive-OR function. Normally, this function is at logic level '1', but it goes 'LOW' to logic level '0' whenever any of its inputs are at logic level '1'. However, another instance where an output '1' is obtained is when both of its inputs are at logic level "1".

The Boolean expression is  $Q = \overline{(A - B)} = A.B + \overline{A.B}$ . It can also be represented as A B

Figure 1.23 shows logic symbol and truth table of exclusive NOR gate.

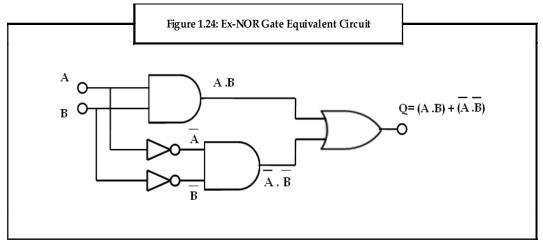

The following figure depicts the Ex-NOR equivalent circuit.

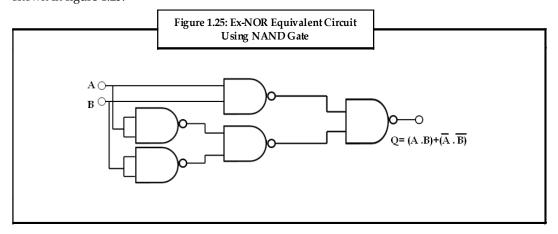

One of the main disadvantages of implementing the Ex-NOR function is that it contains three different types of logic gates which are AND, NOT, and OR gate within its basic design. One simpler way of producing the Ex-NOR function from a single gate type is to use NAND gates as shown in figure 1.25.

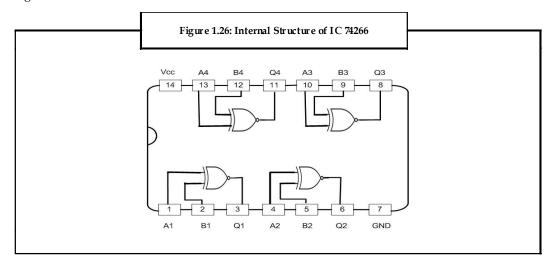

Figure 1.26 shows the internal structure of IC 74266.

Figure 1.26 depicts how EX-NOR gates are placed within an IC. In the figure, pin number 1, 2, 4, 5, 9, 10, 12, and 13 are the inputs to the EX-NOR gate, while 3, 6, 8, and 11 are the EX-NOR outputs. Pin number 7 is connected to ground and pin number 14 is connected to the power supply.

We can classify integrated circuits as follows:

- 1. *Small Scale Integration (SSI):* It contains up to 10 transistors or a few gates within a single package such as AND, OR, and NOT gates.

- Medium Scale Integration (MSI): It contains between 10 and 100 transistors or gates within a single package and performs digital operations such as adders, decoders, counters, flip-flops, and multiplexers.

- Large Scale Integration (LSI): It contains between 100 and 1000 transistors or hundreds of gates and performs specific digital operations on I/O chips, memory, arithmetic, and logic units.

- 4. Very-Large Scale Integration (VLSI): It contains between 1,000 and 10,000 transistors or thousands of gates and performs computational operations such as processors, large memory arrays, and programmable logic devices.

- Super-Large Scale Integration (SLSI): It contains between 10,000 and 100,000 transistors within

a single package and performs computational operations like microprocessor chips, microcontrollers, and basic calculators.

### 1.3 Summary

- Binary codes are classified into many forms like weighted codes, reflective codes, sequential codes, alphanumeric codes, and so on.

- Alphanumeric codes include ASCII code and EBCDIC code.

- There are various logic gates in digital electronics like AND gate, OR gate, NOT gate, NAND gate, NOR gate, and so on, which have their own significance in digital electronics.

- NAND gate and NOR gate are called universal gates as other basic gates can be constructed using these gates.

1.4 Keywords

Boolean Expression: An expression that produces a Boolean value as a result.

Integrated Circuit: Complex circuits that are etched onto tiny chips of semiconductor.

*Micro-controller*: A computer-on-a-single integrated circuit containing a processor core, memory, and programmable input/output peripherals.

RTL: Resistor Transistor Switches.

### 1.5 Self Assessment

- 1. State whether the following statements are true or false:

- (a) Alphanumeric code is mainly used with large computer systems like mainframe computers.

- (b) The Boolean expression for NOR gate is denoted as Q = A+B.

- (c) The Ex-NOR function contains three different types of logic gates which are AND, NOT and OR gate within its basic design.

- 2. Fill in the blanks:

| (a) | Digital data | is represented, | stored, | and | transmitted | as | groups | of | binary | digits | which |

|-----|--------------|-----------------|---------|-----|-------------|----|--------|----|--------|--------|-------|

|     | are called   |                 | •       |     |             |    |        |    |        |        |       |

- (b) In \_\_\_\_\_ code, each decimal digit is represented by a 4-bit binary number.

- (c) The Boolean expression for OR gate is denoted as \_\_\_\_\_

- 3. Select a suitable choice for every question:

- (a) Gray codes are an example of which of the following codes:

- (i) Weighted codes

- (ii) Non-weighted codes

- (iii) Reflective codes

- (iv) Sequential codes

- (b) Which of the following ICs contain up to 10 transistors or a few gates within a single package such as AND, OR, and NOT gates.

- (i) SSI

- (ii) MSI

- (iii) LSI

- (iv) VLSI

### 1.6 Review Questions

- 1. "The digital logic gate is the building block from which all digital electronic circuits and microprocessor based systems are built." Discuss with the help of circuit diagrams.

- 2. "The Boolean expression for AND gate is A.B = Q." Elaborate.

- "NAND gate is a combination of AND gate with an inverter or NOT gate connected together in series." Elaborate.

### **Answers: Self Assessment**

- 1. (a) False

- (b) False

- (c) True

- 2. (a) Bits

- (b) BCD

- (c) Q = A + B

- 3. (a) Non-weighted code

- (b) SSI

### Notes 1.7 Further Readings

Radhakrishnan, T., & Rajaraman, V. (2007). Computer Organization and Architecture. New Delhi :Rajkamal Electric Press. Godse, A.P., & Godse D.A. (2008). Digital Electronics, 3rd ed. Pune: Technical Publications.

http://nptel.iitm.ac.in/courses/Webcourse-contents/IIT-KANPUR/esc102/node32.html

http://www.upscale.utoronto.ca/IYearLab/digital.pdf

$http://www.electronicdesignworks.com/digital\_electronics/multiplexer/multiplexer.htm$

http://www.scribd.com/doc/26296603/DIGITAL-ELECTRONICS-demultiplexer

### **Unit 2: Devices Used in Digital Electronics**

### CONTENTS

Objectives

Introduction

- 2.1 Combinational Circuit and Sequential Circuit

- 2.2 Latches and Flip-flops

- 2.2.1 Latches

- 2.2.2 Flip-flops

- 2.3 Registers

- 2.3.1 Data Register

- 2.3.2 Shift Register

- 2.4 Counters

- 2.4.1 Synchronous Counters

- 2.4.2 Asynchronous Counters

- 2.5 Multiplexer

- 2.6 Demultiplexer

- 2.7 Decoder and Encoder

- 2.7.1 Binary Decoder

- 2.7.2 3 to 8 Decoder

- 2.7.3 Encoder

- 2.8 Summary

- 2.9 Keywords

- 2.10 Self Assessment

- 2.11 Review Questions

- 2.12 Further Readings

### **Objectives**

After studying this unit, you will be able to:

- Differentiate between combinational and sequential circuits

- Explain latches and flip-flops

- Discuss the working of registers and counters

- Describe the functions of multiplexers and demultiplexers

- Identify the features of an encoder and a decoder

### Introduction

Various devices are used in digital electronics. In the previous unit, we discussed logic gates which are devices used to implement basic logical expressions.

Electronic gadgets, despite their complexity operate using basic rules and circuits, which are discussed in this unit. These circuits and rules are applicable to computer organization as well.

We will also discuss about latches and flip-flops, registers, counters, multiplexer, de-multiplexer, and encoder and decoder.

### 2.1 Combinational Circuit and Sequential Circuit

There are two types of circuits that can be constructed using logic gates. They are:

- 1. Combinational circuits

- 2. Sequential circuits

Combinational Circuits: A circuit in which the output/outputs depend on the present state of combination of the logic inputs is called as combinational circuits. These circuits do not consider past state of inputs. Logic gates are the basic building blocks of these circuits. Multiplexers, demultiplexers are combinational circuits.

*Sequential Circuits:* A circuit in which the output/outputs depend on both the present state and past state of input is called as sequential circuit. Flip-flops are the basic building block of a sequential circuit. Sequential circuits have a memory unit which stores the past state of inputs. Sequential circuits can be synchronous or asynchronous.

### 2.2 Latches and Flip-flops

Just as gates are the building blocks of combinatorial circuits, flip-flops are the building blocks of sequential circuits. Gates are built directly from transistors and flip-flops are built from latches.

The output of latches and flip-flops depends not only on the current inputs but also on previous inputs and outputs. One of the contrasting features between a latch and a flip-flop is that a latch does not have a clock signal, whereas a flip-flop always has clock signals.

### 2.2.1 Latches

A latch is a device with exactly two stable states and these states are high-output and low-output. A latch has a feedback path, to retain the information. Hence, latches can be memory devices and can store one bit of data. As the name suggests, latches can be used to "latch onto" information and store it in the required place. One of the most commonly used latches is the SR latch.

### **SR Latch**

An SR latch is an asynchronous device. An SR latch does not depend on control signals but depends only on the state of the S and R inputs. An SR latch can be constructed by interconnecting two NOR gates with a cross-feedback loop. SR latches can also be formed by interconnecting NAND gates but the inputs are swapped and negated.

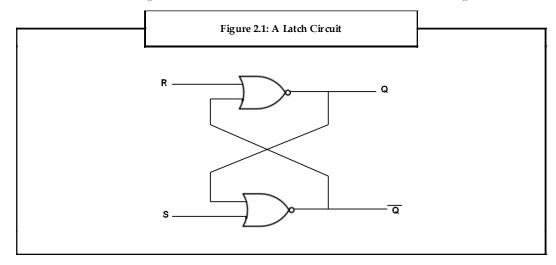

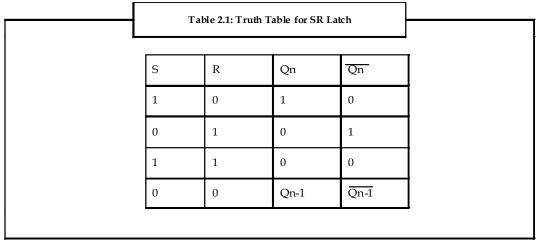

A simple SR latch circuit is shown in the figure 2.1, where the inputs S and R represents 'set' and 'reset'. The current output of a latch is dependent on the state of the latch. Thus, the output at  $n^{th}$  instant represented as  $Q_n$  is dependent on output at  $(n-1)^{th}$  instant represented by  $Q_n-1$ .

The table 2.1 shows the truth table for SR latch.

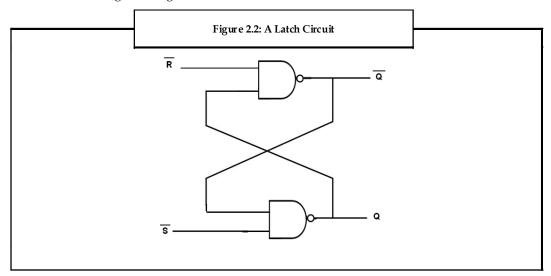

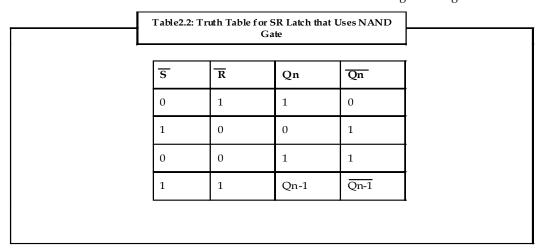

Similar SR latch can be constructed using NAND gates. The figure 2.2 depicts how an SR latch can be constructed using NAND gate.

The table 2.2 shows the truth table for an SR latch that is constructed using NAND gate.

This truth table shows the working of the SR latch.

*Notes* SR latch stores the last state of the inputs that is, it remembers which of the two inputs, 's' or 'r', last had the value of 1.

*Task* Using the concept of SR latch, find out the truth table for gated SR latch.

### 2.2.2 Flip-flops

We know that latches are asynchronous elements, which means that the output varies when the input changes. But most computers have synchronous elements. Synchronous elements are the elements in which the outputs of all the sequential circuits change simultaneously according to the clock signal.

A flip-flop is therefore a synchronous version of the latch.

### Set-Reset (SR) Flip-flop

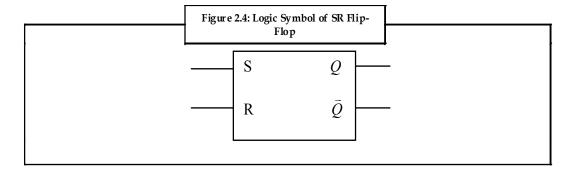

The SR flip-flop has two inputs namely, a 'Set' input and a 'Reset' input. The two outputs of SR flip-flop are: the main output Q and its complement  $\overline{Q}$ .

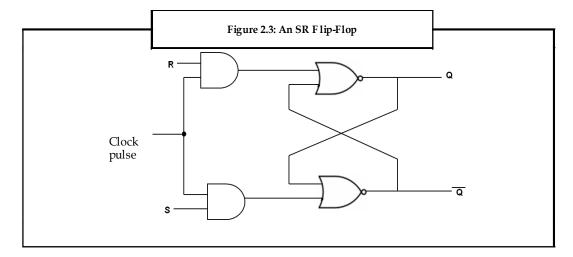

The figure 2.3 depicts the circuit diagram of an SR flip-flop.

The truth table of SR flip flop is shown in table 2.3.

| Table 2.3: Truth Table of SR Flip Flop |   |                              |                                           |   |

|----------------------------------------|---|------------------------------|-------------------------------------------|---|

| S                                      | R | $Q_{\scriptscriptstyle N-1}$ | $\overline{Q}_{\scriptscriptstyle N}$ , 1 |   |

| 0                                      | 0 | $Q_{ m N}$                   | $\overline{Q}$ N                          |   |

| 0                                      | 1 | 0                            | 1                                         |   |

| 1                                      | 0 | 1                            | 0                                         |   |

| 1                                      | 1 | Indet                        | erminate                                  |   |

|                                        |   |                              |                                           | • |

A pair of cross-coupled NOR gates is used to represent an SR flip-flop, wherein, the output of one gate is connected to one of the two inputs of the other gate and vice versa. The free input of one NOR gate is 'R' while the free input of the other gate is 'S'.

The input 'R' produces the output Q and the gate with the 'S' input produces the output  $\bar{Q}$ .

The logic symbol of SR flip-flop is shown in figure 2.4.

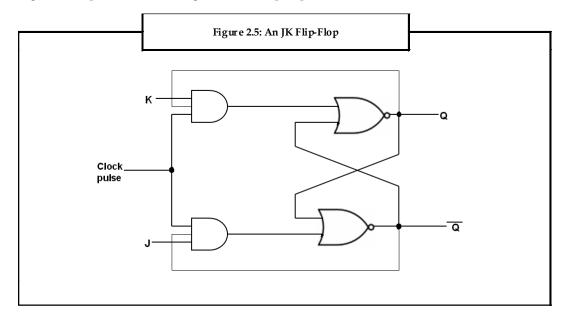

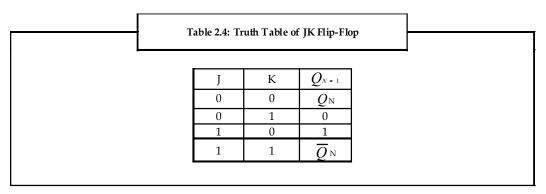

### JK Flip-flop

In JK flip-flop, apart from the states of its inputs, the output is determined by its present output state as well. In the JK flip-flop, the 'S' input is called the 'J' input and the 'R' input is called the 'K' input. The output of the JK flip-flop does not change if both 'J' and 'K' are '0'. However, if both the inputs are '1', then the output toggles to its complement.

Figure 2.5 depicts the circuit diagram of a JK flip-flop.

The truth table of JK flip-flop is shown in table 2.4.

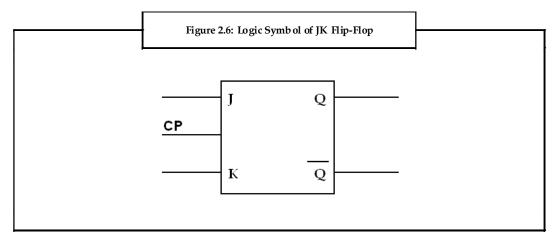

The logic symbol for JK flip-flop is shown in figure 2.6.

### D Flip-flop

The D flip-flop is a clocked flip-flop with a single digital input 'D'. Every time a D flip-flop is clocked, its output follows the state of 'D'.

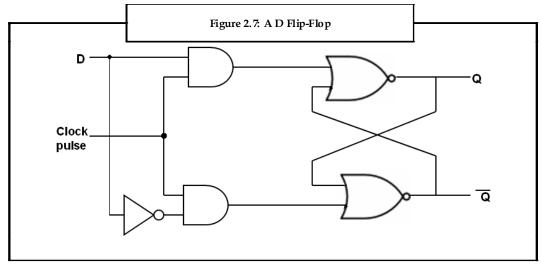

Figure 2.7 depicts the circuit diagram of a D flip-flop.

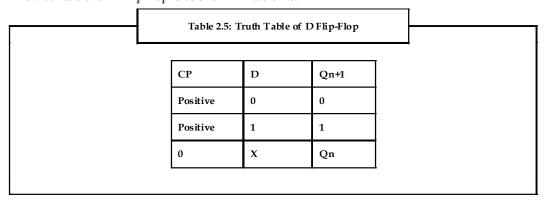

The truth table for D flip-flop is as shown in table 2.5.

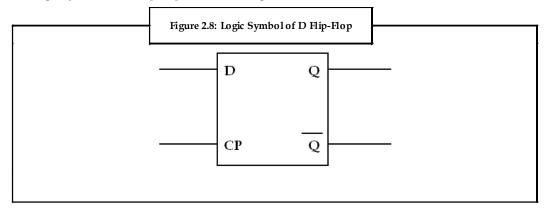

The logic symbol for D flip-flop is shown in figure 2.8.

### T Flip-flop

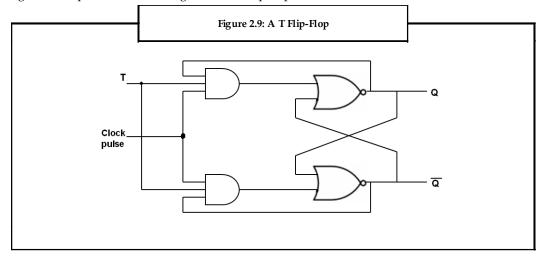

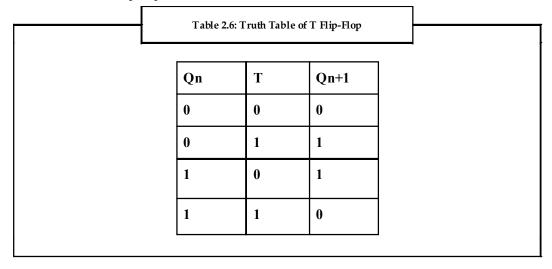

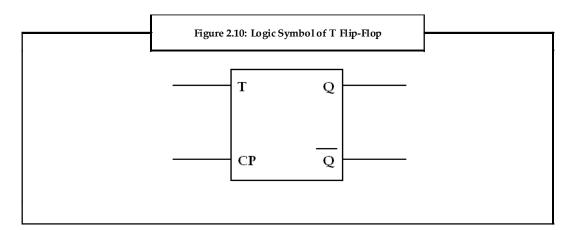

The T flip-flop is also known as toggle flip-flop. It is a modification of the JK flip-flop. The T flip-flop is obtained by connecting both inputs of a JK flip-flop that is, T flip-flop is obtained by connecting the inputs 'J' and 'K' together. When T = 0, both AND gates are disabled. Hence, there is no change in the output. When T = 1, the output toggles.

Figure 2.9 depicts the circuit diagram of a D flip-flop.

The truth table of T flip-flop is shown in table 2.6.

The logic symbol of T flip-flop is shown in figure 2.10.

2.3 Registers Notes

Flip-flops are the binary cells that are capable of storing one bit information. The group of flip-flops can be used to store a word, which is called register. Since flip flops can store 1-bit information, an n-bit register has a group of n flip-flops and is capable of storing binary information containing n-bits.

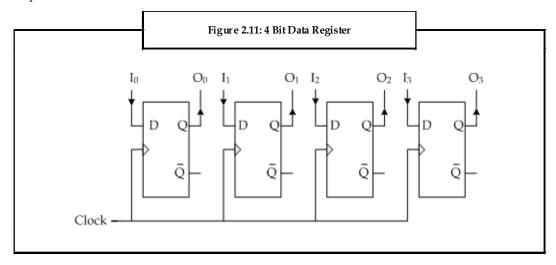

#### 2.3.1 Data Register

Data register is the simplest type of register that is used for the temporary storage of a data word. In its simplest form, it consists of a set of n-D flip-flops, which share a common clock pulse. All the digits that are present in the n-bit data word are connected to the data register by an n-line data bus. The following figure depicts a four bit data register, implemented with four D flip-flops.

Since all the flip-flops change state at the same time, the data register can be called as a synchronous device. The number of flip-flops in a register determines its total storage capacity. Therefore, when the first clock pulse arrives, the stored binary information becomes

QAQBQCQD = ABCD

#### 2.3.2 Shift Register

Another common form of register used in many types of logic circuits is shift register. It is a set of flip-flops (usually D latches or S-R flip-flops) connected together in a series such that the output of one becomes the input of the next, and so on. It is called a shift register because the data is shifted through the register by one bit position on each clock pulse.

Let us next discuss the modes of operation of shift registers.

## Notes Serial-In Serial-Out Shift Register

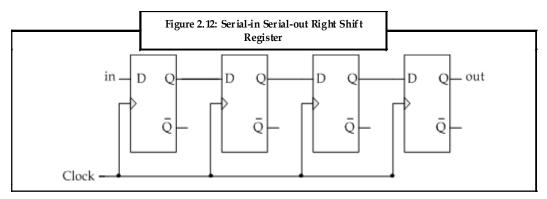

The direction of shifting of data determines the 'serial-in serial-out' shift register into right shift and left shift register. The figure 2.12 shows a 'serial-in serial-out' right shift register.

During the first clock pulse, the signal on the data input is latched in the first flip-flop. During the next clock pulse, the contents of the first flip-flop are stored in the second flip-flop, and the signal which is present at the data input is stored in the first flip-flop, and so on. Because the data is entered one bit at a time, we call it as a serial-in shift register. If there is only one output, and data leaves the shift register one bit at a time, then it is also a serial-out shift register.

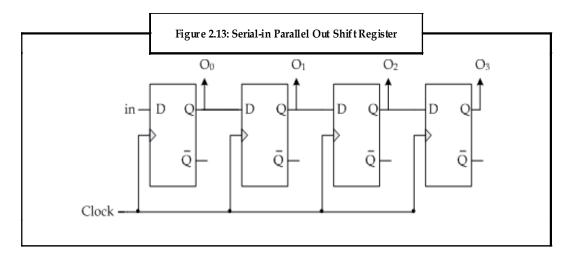

#### Serial-In Parallel Out Shift Register

The 'preset' and 'clear' input commands can be provided to the flip-flops to obtain a parallel input. The parallel loading of the flip-flop can be synchronous (that is, it occurs with the clock pulse) or asynchronous (independent of the clock pulse), depending on the design of the shift register. The outputs of each flip-flop produce a parallel output.

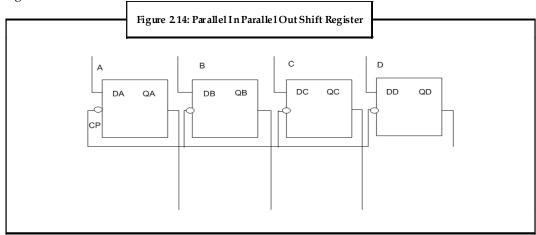

#### Parallel In Parallel Out Shift Register

**Notes**

In 'parallel in parallel out' register there is simultaneous entry of all data bits and the bits appear on parallel outputs simultaneously. The following figure shows a 'parallel in parallel out' shift register.

## 2.4 Counters

A counter is a register which is capable of counting the number of clock pulses arriving at its clock input. There are two types of counters namely, synchronous and asynchronous counters. As the common clock in a synchronous counter is connected to all of the flip-flop, they are clocked simultaneously. In asynchronous counter, the first flip-flop is clocked by the external clock pulse and then each successive flip-flop is clocked by the Q or  $\overline{Q}$  output of the previous flip-flop.

#### 2.4.1 Synchronous Counters

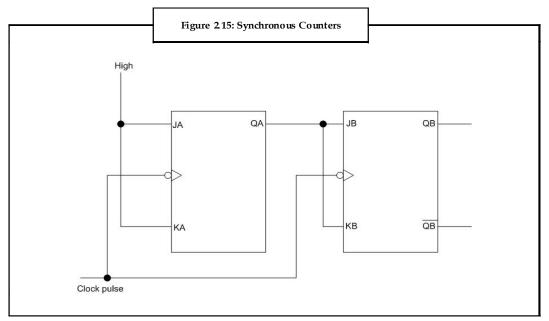

Figure 2.15 depicts a synchronous counter.

Here, the clock signal is connected in parallel to clock inputs of all the flip -flops. Initially, we assume that QA = QB = 0. When positive edge of the first clock pulse is applied, flip-flop A will toggle, whereas flip-flop B output will remain zero because JB = KB = 0. After first clock pulse,

QA = 1 and QB = 0. After second clock pulse, QA = 0 and QB = 1. After the fourth clock pulse the counter recycles back to its original state.

#### 2.4.2 Asynchronous Counters

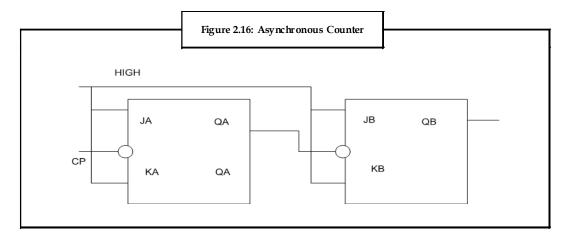

An asynchronous counter consists of a series connection of complementing flip-flops, with the output of each flip-flop connected to the clock input of the next higher order flip-flop. To obtain a complementing flip-flop a JK flip flop can be used by connecting the J and K inputs together. The figure 2.16 shows a 2-bit asynchronous counter using JK flip-flops.

# 2.5 Multiplexer

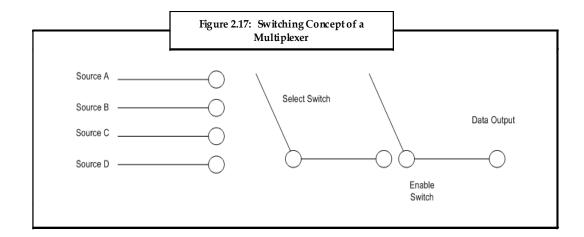

A multiplexer is a digital switch which allows digital information from several sources to be routed onto a single output line. A set of selection lines control the selection of a particular input line. Therefore, a multiplexer is a multiple-input and single-output switch. It provides the digital equivalent of an analog selector switch.

A multiplexer is also called as data selector as it accepts many digital data inputs and selects one of them at any given time to pass onto the output. In some cases, two or more multiplexers are enclosed within an IC package. Figure 2.17 depicts the switching concept of a multiplexer.

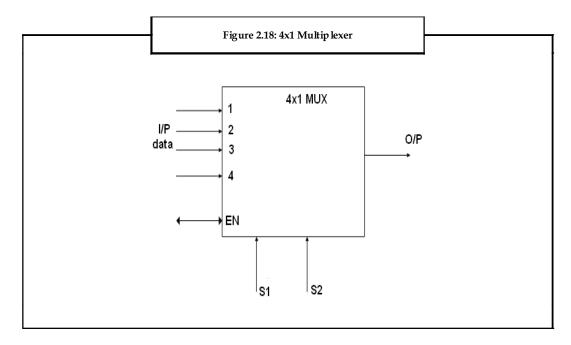

Figure 2.18 depicts a 4 to 1 line multiplexer.

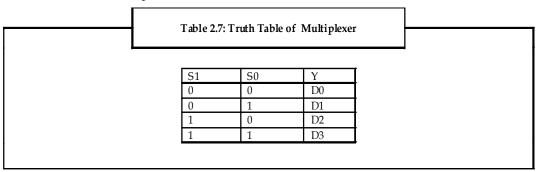

The truth table of a multiplexer circuit is shown in table 2.7.

*Example:* 74xx151 is an 8 to 1 multiplexer which has 8 inputs and two outputs. One of the outputs is an active high output and the other is an active low output. These circuits are used mostly in digital systems of all types, such as data selection, data routing, operation sequencing, parallel-to-serial conversion, waveform generation, and logic-function generation.

# Notes 2.6 Demultiplexer

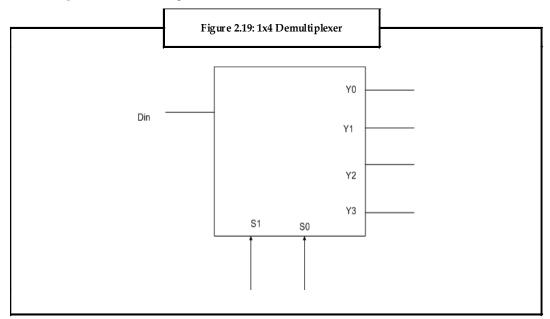

A circuit that receives information on a single line and transmits the information on any of the  $2^n$  possible output lines is called as a demultiplexer. Therefore, a demultiplexer is called a single-input multiple-output switch. The values of n selection lines control the selection of specific output line.

A demultiplexer is shown in figure 2.19.

The truth table of a demultiplexer circuit is shown in table 2.8.

|        |    |    | 2.8: Truth Ta |    | •  |    |    |

|--------|----|----|---------------|----|----|----|----|

|        |    |    |               |    |    |    |    |

| Enable | S1 | S0 | Din           | Y0 | Y1 | Y2 | Y3 |

| 0      | X  | X  | X             | 0  | 0  | 0  | 0  |

| 1      | 0  | 0  | 0             | 0  | 0  | 0  | 0  |

| 1      | 0  | 0  | 1             | 1  | 0  | 0  | 0  |

| 1      | 0  | 1  | 0             | 0  | 0  | 0  |    |

| 1      | 0  | 1  | 1             | 0  | 1  | 0  | 0  |

| 1      | 1  | 0  | 0             | 0  | 0  | 0  | 0  |

| 1      | 1  | 0  | 1             | 0  | 0  | 1  | 0  |

| 1      | 1  | 1  | 0             | 0  | 0  | 0  | 0  |

| 1      | 1  | 1  | 1             | 0  | 0  | 0  | 1  |

A demultiplexer is used extensively in clock demultiplexer, security monitoring system, synchronous data transmission system, and so on.

## 2.7 Decoder and Encoder

A decoder is a multiple input, multiple output logic circuit. A decoder converts coded inputs into coded outputs, where the input and output codes are different. Often, the input code has fewer bits than the output code. Each input code word produces a different output code word. The following figure shows the general structure of the decoder circuit which shows that n inputs produce  $2^n$  possible outputs. The  $2^n$  output values are from 0 through  $2^{n-1}$ . Usually, a decoder is provided with enabled inputs to activate decoded output based on data inputs. When any one enabled input is unasserted, all outputs of decoder are disabled.

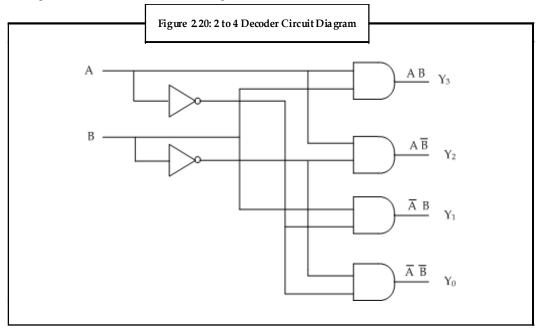

## 2.7.1 Binary Decoder

**Notes**

A binary decoder is a decoder which has an n-bit binary input code and one activated output which is selected from  $2^n$  output codes. This decoder is applicable in instances where it is necessary to activate exactly one of  $2^n$  outputs based on an n-bit input value.

In a 2 to 4 decoder, 2 inputs are decoded into four outputs, each output representing one of the minterms of the 2 input variables. The two inverters provide the complement of the inputs and each one of the four AND gates generate one of the minterms.

The figure 2.20 illustrates the circuit diagram of a 2 to 4 decoder.

Table 2.9 shows the truth table for a 2 to 4 decoder.

|        | Tab | ole 2.9: Trutl | h Table of a 2 | to 4 Decode | r  |    |

|--------|-----|----------------|----------------|-------------|----|----|

| Inputs |     |                | Outputs        | ,           |    |    |

| EN     | A   | В              | Y3             | Y2          | Y1 | Y0 |

| 0      | X   | X              | 0              | 0           | 0  | 0  |

| 1      | 0   | 0              | 0              | 0           | 0  | 1  |

| 1      | 0   | 1              | 0              | 0           | 1  | 0  |

| 1      | 1   | 0              | 0              | 1           | 0  | 0  |

| 1      | 1   | 1              | 1              | 0           | 0  | 0  |

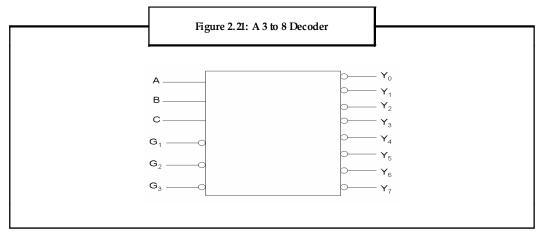

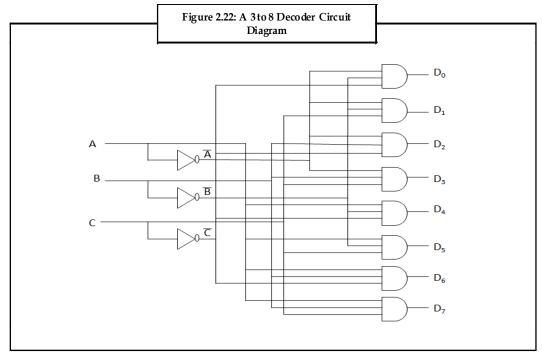

#### 2.7.2 3 to 8 Decoder

The 74x138 is a 3 to 8 decoder. It accepts three binary inputs, namely A, B, and C and it provides eight individual active low outputs (Y0-Y7) when enabled. The device has three enable inputs, that is, two active low and one active high.

The figure 2.21 depicts a 3 to 8 decoder.

Figure 2.22 depicts the circuit diagram of a 3 to 8 decoder.

Table 2.10 shows the truth table of a 3 to 8 decoder.

|   |   | L  |                |    |                |    |                |    |                |                |

|---|---|----|----------------|----|----------------|----|----------------|----|----------------|----------------|

| A | В | Тс | D <sub>0</sub> | D1 | D <sub>2</sub> | D3 | D <sub>4</sub> | D5 | D <sub>6</sub> | D <sub>7</sub> |

| 0 | 0 | 0  | 1              | 0  | 0              | 0  | 0              | 0  | 0              | 0              |

| 0 | 0 | 1  | 0              | 1  | 0              | 0  | 0              | 0  | 0              | 0              |

| 0 | 1 | 0  | 0              | 0  | 1              | 0  | 0              | 0  | 0              | 0              |

| 0 | 1 | 1  | 0              | 0  | 0              | 1  | 0              | 0  | 0              | 0              |

| 1 | 0 | 0  | 0              | 0  | 0              | 0  | 1              | 0  | 0              | 0              |

| 1 | 0 | 1  | 0              | 0  | 0              | 0  | 0              | 1  | 0              | 0              |

| 1 | 1 | 0  | 0              | 0  | 0              | 0  | 0              | 0  | 1              | 0              |

| 1 | 1 | 1  | 0              | 0  | 0              | 0  | 0              | 0  | 0              | 1              |

2.7.3 Encoder Notes

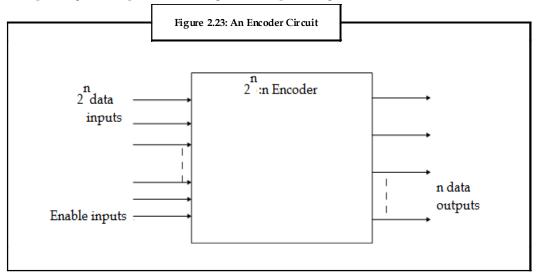

A digital circuit that performs the inverse operation of a decoder is called as an encoder. It has  $2^n$  input lines and n output lines. In an encoder, the output lines generate the binary code corresponding to the input value. The figure 2.23 depicts the general structure of an encoder circuit.

#### **Decimal to BCD Encoder**

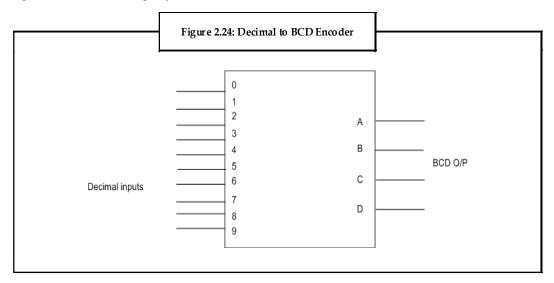

The decimal to BCD encoder has ten input lines and four output lines. The input for the encoder is the decoded decimal data and encoded BCD is the output available on the four output lines. The figure 2.24 shows the logic symbol for decimal to BCD encoder IC.

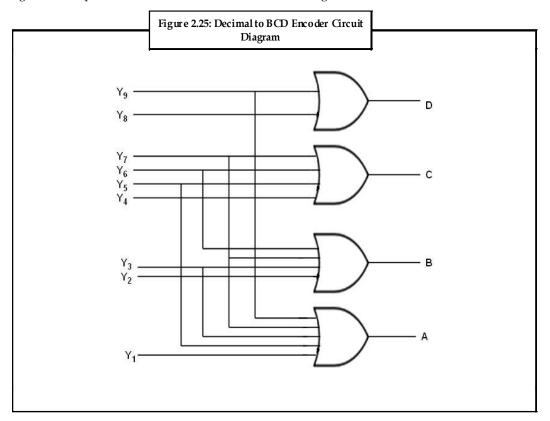

Figure 2.25 depicts the decimal to BCD encoder circuit diagram.

Table 2.11 shows the truth table for a BCD encoder.

|                       |    |    | <u> </u>       |                |                |    |                |    | , |   |   |   |     |

|-----------------------|----|----|----------------|----------------|----------------|----|----------------|----|---|---|---|---|-----|

| <b>Y</b> <sub>1</sub> | Y2 | Y3 | Y <sub>4</sub> | Y <sub>5</sub> | Y <sub>6</sub> | Y7 | Y <sub>8</sub> | Y9 | D | С | В | A | BCD |

| 0                     | 0  | 0  | 0              | 0              | 0              | 0  | 0              | 0  | 0 | 0 | 0 | 0 | 0   |

| 1                     | 0  | 0  | 0              | 0              | 0              | 0  | 0              | 0  | 0 | 0 | 0 | 1 | 1   |

| 0                     | 1  | 0  | 0              | 0              | 0              | 0  | 0              | 0  | 0 | 0 | 1 | 0 | 2   |

| 0                     | 0  | 1  | 0              | 0              | 0              | 0  | 0              | 0  | 0 | 0 | 1 | 1 | 3   |

| 0                     | 0  | 0  | 1              | 0              | 0              | 0  | 0              | 0  | 0 | 1 | 0 | 0 | 4   |

| 0                     | 0  | 0  | 0              | 1              | 0              | 0  | 0              | 0  | 0 | 1 | 0 | 1 | 5   |

| 0                     | 0  | 0  | 0              | 0              | 1              | 0  | 0              | 0  | 0 | 1 | 1 | 0 | 6   |

| 0                     | 0  | 0  | 0              | 0              | 0              | 1  | 0              | 0  | 0 | 1 | 1 | 1 | 7   |

| 0                     | 0  | 0  | 0              | 0              | 0              | 0  | 1              | 0  | 1 | 0 | 0 | 0 | 8   |

| 0                     | 0  | 0  | 0              | 0              | 0              | 0  | 0              | 1  | 1 | 0 | 0 | 1 | 9   |

## 2.8 Summary

- Binary codes are classified into many forms like weighted codes, reflective codes, sequential codes, alphanumeric codes, and so on.

- There are various logic gates in digital electronics like AND gate, OR gate, NOT gate, NAND gate, NOR gate, and so on which have their own significance.

- The output of latches and flip-flops depends not only on the current inputs but also on previous inputs and outputs.

- The group of flip-flops can be used to store a word which is called a register.

A counter is a register which is capable of counting the number of clock pulses arriving at its clock input. Notes

- A multiplexer is a digital switch which allows digital information from several sources to be routed onto a single output line.

- A demultiplexer is a circuit that receives information on a single line and transmits the same information on any of the 2<sup>n</sup> possible output lines.

- A multiple input, multiple output logic circuit is called as a decoder. It converts coded inputs into coded outputs.

- An encoder has 2<sup>n</sup> input lines and n output lines.

# 2.9 Keywords

*Clock Pulse*: A circuit in a processor that generates a regular sequence of electronic pulses used to synchronize operations of the electronic system.

Register: An electronic component that offers a known resistance to the flow of electricity.

*Switch*: A device that directs incoming data from any of multiple input ports to the specific output port.

## 2.10 Self Assessment

| <ol> <li>State whether the following statements are true</li> </ol> | e or tals | se: |

|---------------------------------------------------------------------|-----------|-----|

|---------------------------------------------------------------------|-----------|-----|

- (a) A decoder has 2<sup>n</sup> input lines and n output lines.

- (b) In a 2 to 4 decoder, 2 inputs are decoded into four outputs, each output representing one of the minterms of the 2 input variables.

- (c) A demultiplexer is used extensively in clock multiplexer, security monitoring system, synchronous data transmission system, and so on.

| 2. | Fill | in the blanks:                                                                                                                            |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|    | (a)  | The decimal to BCD encoder has ten input lines and output lines.                                                                          |

|    | (b)  | A multiplexer is also called as as it accepts many digital data inputs and selects one of them at any given time to pass onto the output. |

|    | (c)  | A counter is a which is capable of counting the number of clock pulses arriving at its clock input.                                       |

| 3. | Sele | ct a suitable choice for every question:                                                                                                  |

|    | (a)  | Apart from the states of its inputs, the output of is determined by its present output state as well.                                     |

|    |      | (i) JK flip-flop                                                                                                                          |

|    |      | (ii) S-R flip-flop                                                                                                                        |

|    |      | (iii) D flip-flop                                                                                                                         |

|    |      | (iv) T flip-flop                                                                                                                          |

|    | (b)  | is a multiple input, multiple output logic circuit.                                                                                       |

|    |      | (i) Decoder                                                                                                                               |

|    |      | (ii) Encoder                                                                                                                              |

|    |      | (iii) Multiplexer                                                                                                                         |

|    |      | (iv) Demultiplexer                                                                                                                        |

# Notes 2.11 Review Questions

- 1. "Flip-flops are built from latches." Discuss.

- 2. "A pair of cross-coupled NOR gates is used to represent an S-R flip-flop." Explain with the help of circuit diagrams.

- 3. "Data register is the simplest type of register which is used for the temporary storage of a data word." Elaborate.

- 4. "Shift registers can be operated in different modes." Discuss.

- 5. "Multiplexer is a multiple-input and single-output switch." Explain with the help of circuit diagrams.

- 6. "Demultiplexer is called a single-input, multiple-output switch." Explain with the help of circuit diagrams.

- 7. "In an encoder, the output lines generate the binary code corresponding to the input value." Elaborate.

#### **Answers: Self Assessment**

- 1. (a) False (b) True (c) False

- 2. (a) Four (b) Data selector (c) Register

- . (a) JK flip-flop (b) Decoder

## 2.12 Further Readings

Radhakrishnan, T., & Rajaraman, V. (2007). Computer Organization and Architecture. New Delhi :Rajkamal Electric Press.

Godse, A.P., & Godse D.A. (2008). Digital Electronics, 3rd ed. Pune: Technical Publications.

http://nptel.iitm.ac.in/courses/Webcourse-contents/IIT-KANPUR/esc102/node32.html

http://www.upscale.utoronto.ca/IYearLab/digital.pdf

$http://www.electronicdesignworks.com/digital\_electronics/multiplexer/multiplexer.htm$

http://www.scribd.com/doc/26296603/DIGITAL-ELECTRONICS-demultiplexer

# Unit 3: Data Representation and Data Transfer

#### CONTENTS

Objectives

Introduction

- 3.11's and 2's Complement

- 3.2 Fixed-Point and Floating-Point Number

- 3.2.1 Decimal Fixed-Point Representation

- 3.2.2 Floating-Point Representation

- 3.3 Register Transfer

- 3.3.1 Bus Transfer

- 3.3.2 Memory Transfer

- 3.4 Microoperation

- 3.4.1 Logic Microoperation

- 3.4.2 Shift Microoperation

- 3.4.3 Arithmetic Logic Shift Unit

- 3.5 Summary

- 3.6 Keywords

- 3.7 Self Assessment

- 3.8 Review Questions

- 3.9 Further Readings

#### **Objectives**

After studying this unit, you will be able to:

- Analyse 1s and 2s complement

- Discuss representation of fixed-point and floating-point numbers

- Discuss register transfer language and microoperations

#### Introduction

We are aware that computer organization deals with the functional units and the interconnectivity among them by specifying the details of its architecture. These details may include instruction set, number of bits used for the representation of different types of data (numbers, characters, etc.), and so on. Any computer's organization relies on the way it represents numbers, character, and other information. This information in an organized form is referred to as data.

The information received are stored in memory or used by the CPU to perform required operations. The information received is either data or instructions. An instruction is a command to perform a specific type of operation and the data are the numbers or encoded characters that are represented by signed integers 0 and 1. These signed integers are called as binary numbers. The basic arithmetic operations such as addition, subtraction, multiplication and division can be performed using the basic data types.

*Notes* Instruction set is the basic set of commands that a microprocessor understands.

## 3.1 1's and 2's Complement

In computers, binary number system is used for storing information as 0's and 1's.

#### 1's Complement

1's complement is a method of representation of negative numbers in computers. A binary number's 1's complement is obtained by inverting all 0s to 1s and all 1s to 0s.

Task Find out 1's complement of (1001)2

#### 2's Complement

2's complement is a method of representation of negative binary numbers in computers. A binary number's 2's complement is obtained by adding 1 to that number's 1's complement.

Example: We can represent -28 in 2's complement as follows:

- 1. Write 28 in binary form. 00011100

- 2. Invert the digits by converting 0's to 1's and 1's to 0's. 11100011

- 3. Add 1 to 11100011

The result is 11100100, which represents -28.

Task Find out 2's complement of (1010 0011)2

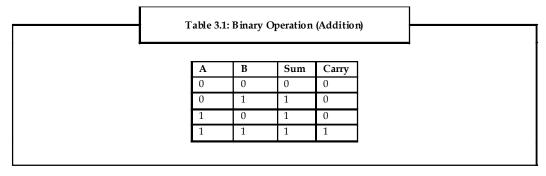

Computer circuits perform different operation on binary number system. Binary operations are the key to perform all basic arithmetic operations, such as addition, subtraction, multiplication, and division. In these operations, the Most Significant Bit (MSB) is reserved to indicate the sign (+ or -). MSB is **0** for positive numbers and **1** for negative numbers. The rules for the binary additions are depicted in the table 3.1.

As per the table 3.1, when two positive numbers are to be added, bit pairs are added, starting from lower-order (right end) bits, going up to the higher-order bits. While adding 1+1, a carry is generated.

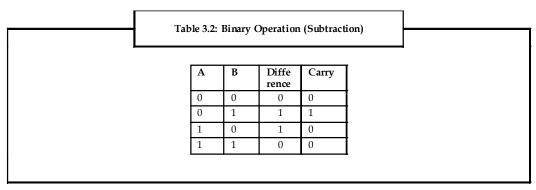

Just like binary additions, binary subtractions also have some rules to be followed. These rules are depicted in table 3.2.

As per table 3.2, when two positive numbers are to be subtracted, bit pairs are subtracted, starting from lower-order (right end) bits, going up to the higher-order bits. The subtraction of binary numbers is similar to the subtraction of decimal numbers. Just as decimal subtraction has the concept of "borrow", subtraction of binary numbers also has the concept of "carry". If you have to subtract a one from a zero, you need to "carry" from the left, just as in decimal subtraction.

Did u know? Signed number representations are required to encode negative numbers in binary number systems.

#### 1's Complement Addition

In 1's complement addition, when two numbers are added, the two binary numbers may be added including the sign bit. If there is a carry after the MSB position, it is called carry-out. In case of signed number addition, it is called end-around-carry. In 1's complement, the representation of positive numbers is identical to sign magnitude system. To represent a negative number, the convention is different and is done by bit- complementing method, meaning replacing 0 by 1 and 1 by 0.

Example: 5 is represented as 10 in bits and -5 is represented as 01

Example: Add (1110), and (1010).

Task Add 6+8 using 1's complement.

## 1's Complement Subtraction

1's complement has two cases of subtraction. These cases are:

- 1. Subtraction of a smaller number from a larger number. The steps followed for subtraction are:

- (a) Determine the 1's complement of the smaller number.

- (b) Add 1's complement to the larger number.

- (c) Add the carry that is obtained, to the result.

Example: Subtract (101011)<sub>2</sub> from (111001)<sub>2</sub>.

- 2. Subtraction of a larger number from a smaller number. The steps followed for this type of subtraction are:

- (a) Determine the 1's complement of the larger number.

- (b) Add 1's complement to the smaller number.

- (c) As the result is in 1's complement, to obtain the required result, the answer is converted to 1's complement with a negative sign.

Example: Subtract (111001), with (101011),

*Notes* 1's complement arithmetic was common in older computers; the PDP-1, CDC 160A and UNIVAC 1100/2200 series are some computers that used ones'-complement arithmetic.

Notes

## 2's Complement Addition

When 2's complement system is used to represent negative numbers, the addition operation is similar to the 1's complement system. The calculation steps that are followed to add using 2's complement include:

- 1. Representing both numbers in signed-2's complement format.

- 2. Adding operands and discard carry-out of the sign bit MSB (if any).

Example:

The result obtained is automatically in signed-2's complement form.

#### 2's Complement Subtraction

The following steps explain subtraction using 2's complement.

If A and B are the numbers that are to be subtracted, A is called as minuend and B is called the subtrahend.

- 1. Represent both numbers in signed-2's complement format.

- 2. Obtain 2's complement of the subtrahend B (which may be in complement form already if it is negative).

- 3. Add it to A.

Example: Subtract 12 from 7.

The result is automatically in signed-2's complement form.

*Notes* The 2's complement system has the following advantage: It is not required for the addition or subtraction circuitry of the 2's complement to examine the signs of the operands to determine whether to perform addition or subtraction.

2's complement has two cases of subtraction. These cases are:

- 1. Subtraction of a smaller number from a larger number. The subtraction steps are:

- (a) The smaller number of 2's complement is determined.

- (b) The bigger number is added with 2's complement.

- (c) The carry is discarded.

Example: Subtract (101011)<sub>2</sub> from (111001)<sub>2</sub>.

- Subtraction of a larger number from a smaller number. The steps for this type of subtraction are:

- (a) The 2's complement of bigger number is determined.

- (b) The 2's complement is added to the smaller number.

- (c) The 2's complement answer is prefixed with negative value to get a true value.

Example: Subtract 69 from 12

Here, 12-69 = 12+(-69)

Subtract 9-2 using 2's complement.

## 3.2 Fixed-Point and Floating-Point Number

Fixed-points are considered as a simple and easy way to represent factorial numbers. The fixed-point numbers use a fixed amount of bits. The term "fixed-point" refers to the decimal point of a number. There is no separate symbol to designate where the decimal point lies. However, in binary, bits can either be 0 or 1.

In floating-point representation, a decimal point number is multiplied by a base value and it is scaled up with an exponent value. The usage of floating-point number is limited when compared to fixed-point number because floating-point number carries a wide range of real numbers values.

#### 3.2.1 Decimal Fixed-Point Representation

Fixed-point representation has a radix point called decimal point. Fixed-point numbers having decimal points at the right end of the number are considered as integers, whereas the fixed-point numbers having decimal points at the left end of the number are considered as fractions. In either case, the decimal point position is fixed because the number stored in the memory is treated as an integer or as a fraction.

The binary numbers that are unsigned are always treated as positive integers and are represented as **0**s in the MSB. As we are aware, the binary numbers that are signed differ for negative numbers and are represented as **1**s in the MSB.

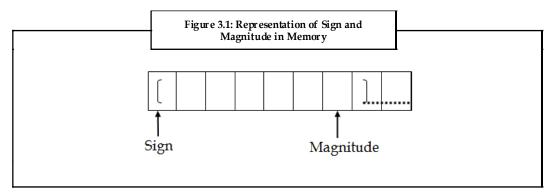

The magnitude of the signed binary numbers can be represented using three approaches. They are:

- 1. Sign and magnitude representation.

- 2. Signed 1's complement representation.

- 3. Signed 2's complement representation.

The following section deals with a brief explanation of these three approaches.

#### Sign and Magnitude Representation

In this approach, the leftmost bit in the number is used for indicating the sign; 0 indicates a positive integer, and 1 indicates a negative integer. The remaining bits in the number give the magnitude of the number.

Example: -2410 is represented as:

1001 1000

In this example, the leftmost bit 1 means negative, and the magnitude is 24.

The magnitude for both positive and negative value is same, but they differ only with their signs.

The range of values for the sign and magnitude representation is from -127 to 127.

Example: 1-sign bit and 7-bit magnitude.

01001001 = +73 0 at the LHS indicates the positive value 10010010 = -18 1 at the LHS indicates the negative value

#### Signed 1's Complement Representation

In signed 1's complement representation, a negative value is obtained by taking the 1's complement of the corresponding positive number. Also, a signed 1's complement method produces end carry during arithmetic operation that cannot be discarded.

The range of values for the signed 1's complement representation is from -127 to 128.

Example: Consider 8-bit numbers for 1's complement.

$(29)_{10} = (00011101)_2 = 000011101$  1's complement for positive value -(29)10 = -(00011101)2 = 111100010 1's complement for negative value

## Signed 2's Complement Representation

In signed 2's complement representation, the 2's complement of a number is found by first taking the 1's complement of that number, then incrementing the result by 1.

The range of values for the signed 2's complement representation is from -128 to 127.

Example:

Consider 8-bit numbers for 2's complement.

$$(29)_{10} = (00011100)_2 = (000011100)_{2s}$$

2's complement for positive value  $-(29)_{10} = -(00011100)_2 = (11110010)_{2s}$  2's complement for negative value

#### 3.2.2 Floating-Point Representation

The floating-point representation is used to perform operations for high range values. The scientific calculations are carried out using floating-point values. To make calculations simple, scientific numbers are represented as follows:

The number 5,600,000 can be represented as  $0.56 * 10^7$

Here, 0.56 is the mantissa and 7 is the value of the exponent.

Similar to the above example, binary numbers can also be represented in the exponential form. The representation of binary numbers in the exponential form is known as floating-point representation. The floating-point representation divides the number in two parts, the left hand side is a signed, fixed-point number called **mantissa** and the right hand side of the number is called the **exponent**. The floating-point values are also assigned with a sign; **0** indicating the positive value and **1** indicating the negative value.

General form of floating-point representation of a binary number:

$$x = (x_0 * 2^0 + x_1 * 2^1 + x_2 * 2^2 + - - - - - + b_{-(n-1)} * 2^{-(n-1)})$$

mantissa \* 2 exponent

In the above syntax, the decimal point is moved left for negative exponents of two and right for positive exponents of two. Both the mantissa and the exponent are signed values allowing for negative numbers and for negative exponents respectively.

Example: Convert 111101.1000110 into floating-point value.

111101.1000110 = 1.111011000110 \* 2<sup>5</sup>

converted to floating-point value.

indicates the negative sign value

In this example, the integer value is converted to floating-point value by shifting the radix point next to the signed integer and scaling up the number to the exponential form by multiplying the value with the base 2. The value remains unchanged and this procedure is called the normalized method.

The floating-point numbers are of two types, which are:

- 1. Normalized and Un-normalized

- 2. Single precision and Double precision

## Normalized and Un-Normalized Floating-Point Numbers

Notes

In normalized floating-point representation, the most significant digit of the mantissa is non-zero. Thus, the number is normalized only if its leftmost digit is non-zero. Normalized floating-point numbers provide the maximum number of possible precisions for the floating-point number.

*Example:* The number 450 is normalized, but the number 000045 is not normalized.

0.0035\*10<sup>5</sup> is un- normalized, whereas 0.35000 \* 10<sup>3</sup> is normalized.

Eight bit numbers are not normalized because of leading 0s. These numbers can be normalized by shifting three places to the left to obtain 10010000 in a number.

Normalized Version representation is shown below:

Value represented = +1.0110... \*26 is a normalized value

Un-normalized version representation is shown below:

Value represented =  $+0.0010110...*2^9$  is an unsigned value.

There is no implicit point to the left of the binary point.

#### Single Precision and Double Precision

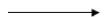

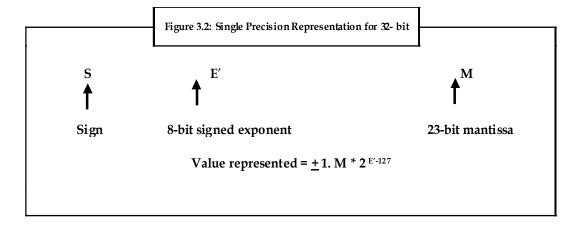

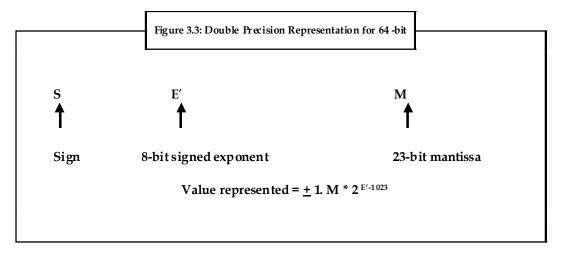

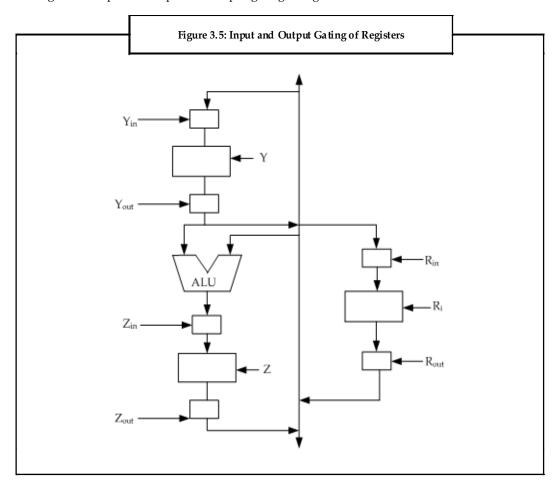

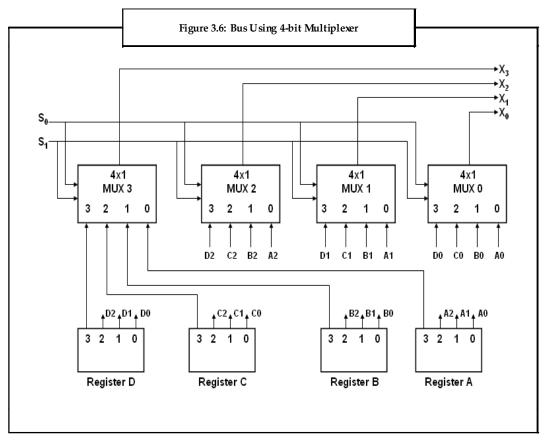

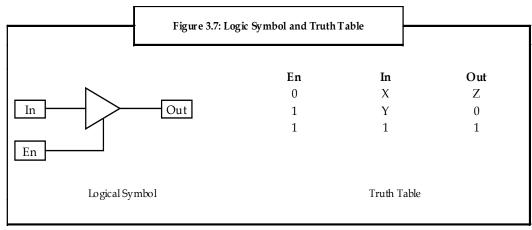

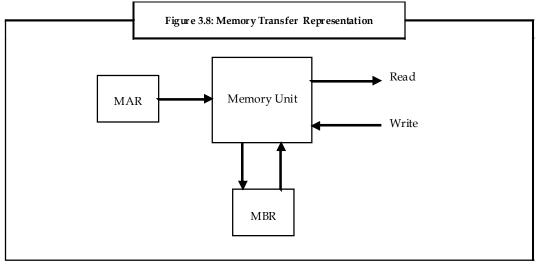

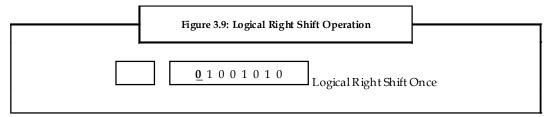

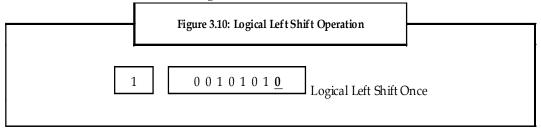

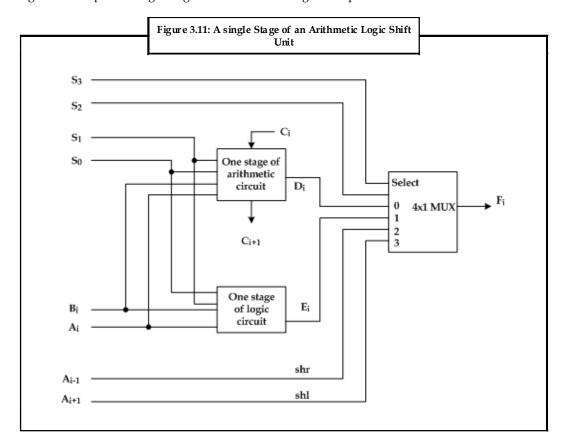

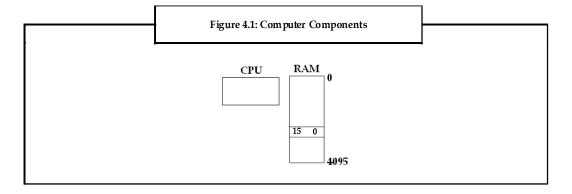

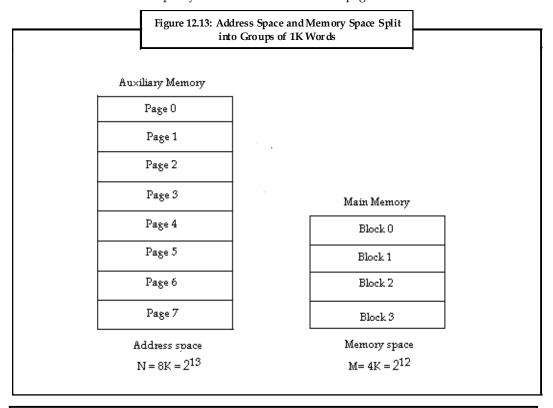

As depicted in the figure 3.2, the 23 bit, which represents the **mantissa** whose most significant bit is always equal to 1, is normalized. This bit is immediate to the left of the binary point. Hence, the 23 bits stored in the **M** field represent the fractional part of the **mantissa** and this 32 bit representation is called the single precision because it occupies a single 32 bit word.